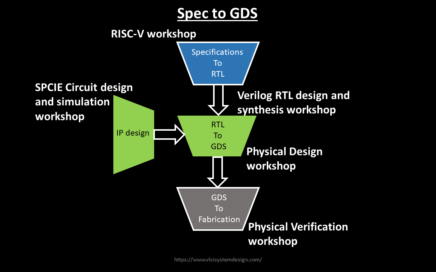

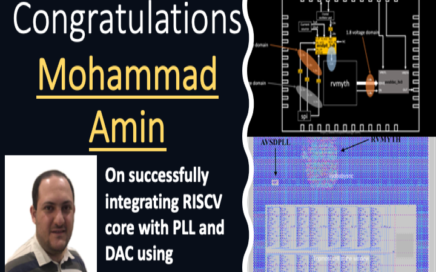

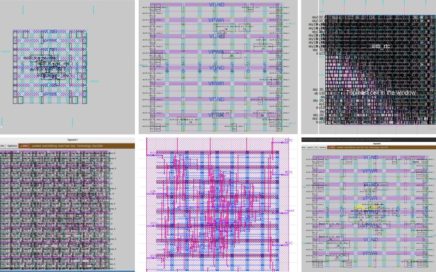

VSD – IIIT Bangalore – Unique example of industry-academia collaboration – 12 chip tapeouts in 2 months

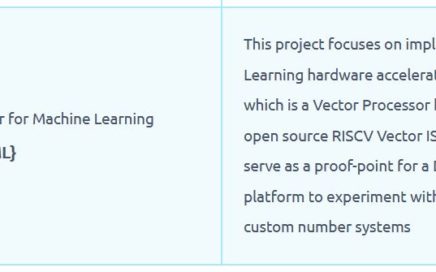

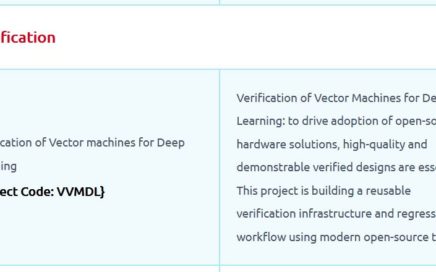

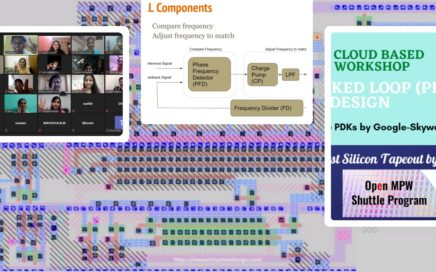

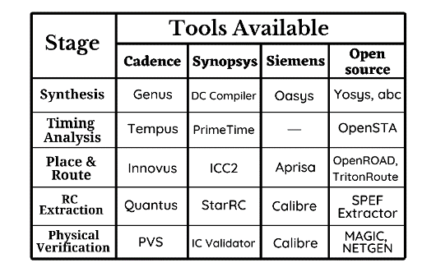

VSD-IIIT Bangalore to set a unique industry-academia model for all colleges across India regarding how tapeout-oriented ASIC design courses can be a part of a full semester curriculum, given the amount of flexibility for curriculum change and mapping to latest industry needs. And thanks to Google/Skywater/efabless for opening up the foundry information, due to which we were able to provide chip design and manufacturing experience to a whole cohort.