designed by VSD Community

Find all repository at

SRAM

Yashwant Moses

GitHub

Comparator IP

Banda Anusha

GitHub

Mixed Signal 10-Bit C2C Digital to Analog Converter

Kavya Agarwal

GitHub

PLL Clock Multiplier IP

Gogoreddy Ravi Kiran Reddy

GitHub

Crack Sensing Circuit

Ritesh Lalwani

GitHub

Mixed signal 2 STEP flash ADC

Aditya Singh

GitHub

Mixed signal 2 STEP flash ADC

Sanampudi Gopala Krishna Reddy

GitHub

Band Gap Reference Circuit (BGR)

Gandi Ajay Kumar

GitHub

10-bit ADC – Analog to Digital Convertor

Aman Hussain

GitHub

10-bit ADC – Analog to Digital Convertor

Kashif Nazeer

GitHub

10-bit ADC – Analog to Digital Convertor

Shaurya Chandra

GitHub

Bandgap

Sumanth Dasari

GitHub

Bandgap

Soundarya Madhuri Royyuru

GitHub

Design of CMOS based Artificial Neural Network

Nalinkumar S

GitHub

Voltage Controlled Oscillator

Sangesh S

GitHub

Low Power Analog Mixed Signal Design of CNN operator for AI Accelerator

Amit Surpur

GitHub

Performance Analysis of Low-Power Power-on-Reset Circuit using SKY130 PDK Technology

Sree Vishnu Varthini S

GitHub

1.8V CMOS Low Drop-Out Regulator Design

Nirvan Tamhane

GitHub

Low Power Operational Amplifier using 130nm Technoloy

Velugoti Ashok Kumar

GitHub

Low-Bit Quantized MAC

Jagadeesh Kumar Anamala

GitHub

Low Dropout Regulator Design for Efficient Power Management in Battery-Powered Systems

Ayesha Parveen

GitHub

Design and Simulation of a CMOS-Based Memristive Crossbar Array with Analog Tanh Activation Function

P K Adithya Das

GitHub

Analog Cryptography

Joshi Aishwarya C

GitHub

Vayu Yantra: “Affordable 32-bit RISC-V Flight Computer: Customizable Control for Aerospace Versatility”

Nahusha K L

Guruprasad

G R Vighneshwar

GitHub

Quantized AI Model

“Real-time Handwritten Digit Recognition using RISC-V”

Dhanvanti Bhavsar

Ankit Mawle

GitHub

Warehouse Automation Robot

“Autonomous Warehouse Efficiency with RISC-V Powered Robotics”

Ashish Ramesh

Sahil Desai

Siddaling Nagavimath

GitHub

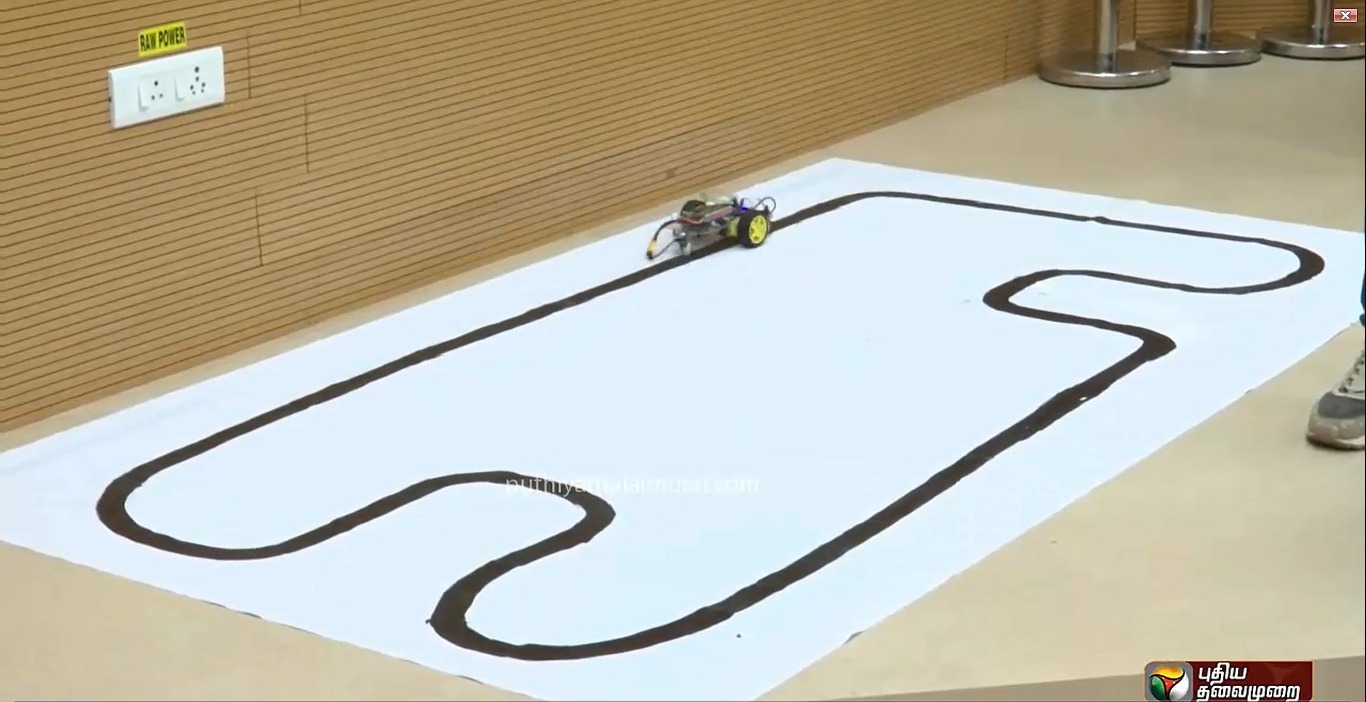

VSD NAVI CAR: “Avoid the Unseen ,the future of mobility”

Rajashekhar Kanukuntla

Vanshika Tanwar

GitHub

Wearable-Haptic-braille-device-for-Blind

Yash Gupta

Daksh Shamra

Divyansh Singhal

GitHub

Smart Hand Mobility Assistive Device for Enhanced Rehabilitation and Daily Assistance

Kushagra Singh

Anshul V Patil

Kafil Abbas Momin

GitHub

Refreshable Braille Display

Sujit Ghantasala

Lokesh Aravapalli

Lohitaksh Maruvada

GitHub

Autonomous Robotic Integration for Automation

Ashish Ramesh

Sahil Parashram Desai

Jonathan Daniel K

GitHub

Smart forest monitoring system

Khushal A

Kishore A

Tejas Neswi

GitHub

OptiPower: AI-Optimized IoT Energy Meter & Switch with Edge & Cloud Intelligence

Shreyas H

Dashami Bhat

Mohammed Saif

GitHub

Long Range Fixed Wing Autonomous Blood Delivery UAV

Nahusha K L

G R Vigneshwar

Guruprasad

GitHub

SmartCane: The Next Generation Navigation Aid for the Visually Impaired

Gajendra Rajak

Sayan Saha

Karthik Milind Patil

GitHub

BLITZ (Blockchain Light Integrity and Tampering Zeroizer)

Rahul Mukundhan

Siddharth Vikram

Shanmukh Praneeth

GitHub

MediSync: Smart Health Monitoring System for Elderly Care with Medication Reminder

Prabu Jayant

Elvis Vincent

Chavi Gupta

GitHub

Fire Detection System

Shriya Gupta

Siddharth Vikram

GitHub

Bluetooth automated smart access

Mahathi R

Joshi Aishwarya Chandrashekhar

GitHub

Hardware Captcha – Home safety system

Sreyas Janamanchi

Chinmay Krishna

GitHub

LiFi Lock

Swetha Murali

PVS Sukeerthi

GitHub

Water Level Indicator

Nagashree wagganavar

Rohan V Poorma

GitHub

LPG Gas Dectector

Srujan siddapurmath

Vishal B

GitHub

Digital clock with alarm functionality

Vignesh Ramesh Rao

Preethi S Aralikatti

GitHub

Traffic Signal Automation System with Ambulance Detection

Skandan M M

Sathvika M

GitHub

Digital Lock System

Yash Sengupta

K.S.V. Rohit

GitHub

Wireless Crowd Monitoring System

Aditya Joshi

Kavyanjali

GitHub

Bluetooth Messenger

Anshu Srinivas

Hitesh K V

GitHub

Soldiers Health Monitoring and GPS Tracking System

Bandaru Jnyanadeep

Bipin Raj C

GitHub

Smart Plant Care using the VSD_Squadron-MINI-BOARD

Kafil Abbas Momin

Kushagra Singh

GitHub

Colorimeter

Shreyas M Iliger

Tushar M

GitHub

RFID-Attendance-System-with-Google-Sheets

Vadiraj Narayan Betageri

Shubham Kallappa Dhabale

GitHub

Morse Code Decoder using VSDSquadron

Shreyash Patukale

Harsha Rampur

GitHub

Advanced Easy to use Burgler Alarm

Nahusha K L

G R Vigneshwar

GitHub

PARKinSENSE

Yash Gupta

Daksh Sharma

GitHub

Water level monitoring and control in water tank

Kaushik M

L Sathya Suryanarayana Sharma

GitHub

Smart irrigation

Priyanshu Kumar Chaudhary

S Nithin

BMSCE, Bangalore

GitHub

MediEase-Simplifying-Health-Management

Advith

Supritha Bekal

(Mangalore Institute of Technology & Engineering, Udupi)

GitHub

“Smart Aquatic”: Smart and automated fish aquarium system

Alwin Dsouza

Prabal Raj

(Mangalore Institute of Technology & Engineering, Udupi)

GitHub

Solar Powered Automated Vacuum Lawn Mower

Shardul Satheskumar

Brunda S Kotian

(RNSIT, Bangalore)

GitHub

Bits n Bytes

Navya Tayi

Shubha Chaugule

(PES University, Bangalore)

GitHub

Reverse Vending Machine

Bobbili Mrudulakshi

Sanjay Barla

RGUKT – IIIT Nuzvid

RGUKT – Srukakulam College

GitHub

Secure Vision

Vanshika Tanwar

E Balakrishna

(Dronacharya Group of Institutions, Greater Noida)

GitHub

TopGun

Vinayak Mishra

Sahil Savanth M

(BMSCE, Bangalore)

GitHub

Melodica

Sujay Samuel Shanthakumar

Samuel Robinson R

(SSN College of Engineering, Chennai)

GitHub

K Tech Sree Kanna

Kanukuntla Rajashekhar

Boddula Navaneeth Kumar

(Kakatiya university, Warangal Mahatma Gandhi University, Nalgonda)

GitHub

Home Automation System with IoT Integration

Shubham Gaikwad

GitHub

Digital Alarm Clock

Iswarya I

GitHub

Anti – theft Compartment

Nitesh Sharma

GitHub

Smart HVAC system

Vartika Barnwal

GitHub

Passcode based Authenticator for Locker

Shant Rakshit

GitHub

Contactless Water Level Controller

Alwin Shaju

GitHub

Automatic street light system

G Lasya Punya Sree

GitHub

Hall effect sensor based Door Alarm system

Amith Bharadwaj

GitHub

Automatic Sanitizer Dispenser

Kanish R

GitHub

Gas leakage detector

Sushma R

GitHub

Rain Alert System

Tushar Mavi

GitHub

Sound based smart switch

Rachana Kaparthi

GitHub

Automatic Roof Controller

Valipreddy Pranathi

GitHub

Automated room lighting control

Emil Jayanth Lal

GitHub

BlindSight Aid

Nancy Gupta

GitHub

Distance measuring

Priyansh Pandya

GitHub

Smart Bin

Lakshmi Sai Niharika Vulchi

GitHub

Blind Sick

Simarjeet Singh Thethi

GitHub

Security alarm system

Arul Vignesh J

GitHub

Temperature activated fan controller

Vaibhav Tiwari

GitHub

Breath_Analyser-Detecting Presence_of_Alcohol

Divyam Satle

GitHub

Fire alarm

Shivangi

GitHub

Touch Sensor Based Bell

Akhil Ganesh Asati

GitHub

Smart Traffic Light

Akul Sinha

GitHub

Conveyor Belt Object Detector

Solanki Pratikkumar Ashokkumar

GitHub

Drip Irrigation system

Kopparthi Dinesh Lingaiah

GitHub

Obstacle Avoiding Car

Sahil Singh Rana

GitHub

Social Distance detection

Pruthvi Parate

GitHub

Display controller

Bhargav D V

GitHub

Industrial Production Line Counter system

Nitish Kumar

GitHub

2 Player Arcade game

Ammula Shiva Kumar

GitHub

Magnetic Intruder Detection System

Aamod B K

GitHub

Smart Home Power System with Burglar Alarm

Saket Gurjar

GitHub

Automated visitor counter

Nalamothu Sai Sampath

GitHub

Heart rate monitor

Yash Dhaarmesh Mogal

GitHub

Hand Dryer

Malobi Mukherjee

GitHub

Home security alarm

Dilli Babu Porlapothula

GitHub

Bidirectional Counter

Pankaj Agrawal

GitHub

Synchronous First In First Out for Memory Storage and Processing

Anmol Shetty

GitHub

Universal Asynchronous Receiver Transmitter Protocol based Hardware Transmitter

Jay Shah

GitHub

Universal Shift Register

Rakshit Bhatia

GitHub

Vending Machine with Change System

Siddhant Nayak

GitHub

Car Parking System

Ishan Desai

GitHub

Parallel input Serial output Shift register

Raj Kachhadiya

GitHub

8 bit BCD counter

Sritam Birtia

GitHub

Johnson counter

Aman Prajapati

GitHub

8-bit Gray code counter

Tejas B N

GitHub

Linear feedback shift register

Ritesh Lalwani

GitHub

Traffic Light Controller

Lokesh Maji

GitHub

LIFO (Last in First out) Buffer

Yash Kothari

GitHub

Three Bit Ring Counter

Arsh Kedia

GitHub

Baud Rate Generator

Rohit Raj

GitHub

PWM (Pulse width modulation) Generator

Himanshu Rai

GitHub

Serial In Parallel Out Shift Register

Aditya Singh

GitHub

Elevator Controller

Nishit Chechani

GitHub

Bidirectional up/down counter

Ujjawal Sharma

GitHub

4 Bit Bidirectional Counter

Sahil Mahajan

GitHub

ASIC design of automatic washing machine

Archan Desai

GitHub

Sequence Detection using Moore FSM

Anshul Mdurwar

GitHub

Sequence Detector 1010 (Without Overlapping) using Mealy Finite State Machine

Anuj Kumar Jha

GitHub

Parking Ticket Vending Machine

Suysh Mishra

GitHub

Parallel in parallel out shift register

Priyanshu

GitHub

Arithmatic Logic Unit

Aashish Tiwary

GitHub

Sequence detector_moore_machine (1011)

G.Ravi Kiran Reddy

GitHub

Pulse Width Modulated Wave Generator with Variable Duty Cycle

Sanampudi Gopala Krishna Reddy

GitHub

RISC-V

Vinay Rayapati

GitHub

Ring Counter

Kavya Agarwal

GitHub

Clock Gating

Vasanthi D R

GitHub

Frequency Divider

Dantu Nandini Devi

GitHub

Real-time clock

Banda Anusha

GitHub

Universal shift register

Debangana Mukherjee

GitHub

101011 Sequence detector _Mealy_Machine

Ajay Kumar

GitHub

PISO shift register

Mahati Basavaraju

GitHub

Ring counter

Ramya S

GitHub

Radix-2 4-Bit Booth’s Multiplier

Yashwant

GitHub

RISC-V based SoC for 8x-PLL and 10-bit DAC calibration using Sky130

Mohammad Amin

SRBIAU

GitHub

“VEZZAL – A Testing Environment for OS-EDA tools”

Sai Charan Lanka

Vardhaman College

GitHub

“Design and Analysis of a RISC-V core with an external Instruction Memory SRAM Using Opensource Tools”

Mufutau Akuruyejo

Gatech

GitHub

SoC design using RISC-V based core and 10-bit DAC Sky130 IP

Mansi Mohapatra

Indira Gandhi Delhi Technical University for Women (IGDTUW)

GitHub

SoC design using RISC-V based core and 10-bit DAC Sky130 IP

Mili Anand

Indira Gandhi Delhi Technical University for Women (IGDTUW)

GitHub

RISC-V based SOC Design with PLL using Open-Source EDA

Balaji Rao Vavintaparthi

BML Munjal University

GitHub

.

Sziklai Pair Amplifier

Sumanto Kar

Fr. Conceicao Rodrigues College of Engg.

GitHub

Current Starved VCO Targeting

Nalinkumar S

Madras Institute of Technology Campus, Anna University

GitHub

Two Stage CMOS Operational Amplifier

R.V.Rohinth Ram

Madras Institute of Technology Campus, Anna University

GitHub

8-bit priority encoder

Mohammad Khalique Khan

Aliah University, Kolkata

GitHub

Design and Analysis of Dickson Charge Pump using CMOS technology

Charaan S

Madras Institute of Technology Campus Anna University

GitHub

Serializer

A Devipriya

Cambridge Institute of Technology, K R Puram, Bangalore

GitHub

The Two Stage CMOS Operational Amplifier with Frequency Compensation

Madhuri Hemant Kadam

Shree L. R. Tiwari College of Engineering

GitHub

.

General Purpose Bandgap

Anmol Purty

M.Tech from National Institute of Technology, Warangal

SKY130

GitHub

10 placeable Standard Cell library design, layout and characterization (just like inv design in workshop) with 4 drive strengths of each. Total 40 standard cells

Harsh Shukla

MS Analog and Mixed Signal Design, Arizona State University

SKY130

GitHub

10bit potentiometric DAC 3.3v analog voltage, 1.8v digital voltage and 1 off-chip external voltage reference

Harshitha Basavaraju

PhD Scholar @ University of Bundeswehr, Munich, Germany

SKY130

GitHub

Lower power current programmable CMOS comparator with hysteresis

Malay Marut Das

EDI Analyst at Miracle Software Systems, Inc., Portland, Oregon, United States

SKY130

GitHub

10bit potentiometric DAC 3.3v analog voltage, 1.8v digital voltage and 1 off-chip external voltage reference

S Skandha Deepsita

PhD Scholar @ IIITDM Kancheepurama

SKY130

GitHub

10bit potentiometric DAC 3.3v analog voltage, 1.8v digital voltage and 1 off-chip external voltage reference

Sameer S Durgoji

B.Tech (Electronics and Communication Engineering), National Institute of Technology Karnataka

SKY130

GitHub

10bit potentiometric DAC 3.3v analog voltage, 1.8v digital voltage and 1 off-chip external voltage reference

Shalini Kanna

Master of Science in Computer Engineering, University of Massachusetts Lowell

SKY130

GitHub

OpenRAM configuration for SRAM (1024 x 32): (32kbits or 4kB), 1.8V and access time is <2.5ns

Shon Pravin Taware

M.Tech. Embedded System and VLSI Design, Shri Guru Gobind Singhji Institute of Engineering and Technology, Vishnupuri, Nanded

SKY130

GitHub

On-chip PLL (avsdpll_3v3) Clock multiplier (pll) (Fclkin – 5MHz to 12Mhz, Fclkout – 40MHz to 100MHz at 1.8v) characterization TCL flow for sky130 tt, ss, ff, sf, fs corners

Subham Mohapatra

Electrical & Electronics undergrad, NIT Karnataka

SKY130

GitHub

General Purpose bandgap

Swarup Pulujkar

Hardware Development Engineer at eZono AG, Germany

SKY130

GitHub

Design of 4KB(1024*32) SRAM 1.8V with operating voltage 1.8v and access time < 2.5ns

Deepak Verma

IIIT Sonepat

SKY130

GitHub

Design of 4KB Static RAM 1.8V (access time <2.5ns) using OpenRAM and Sky130 node

Pradeepkumar S K

Kalpataru Institute of Technology, Tiptur, Karnataka

SKY130

GitHub

PLL IP to be tested is included in the SOIC-24 package to communicate with external circuitry present in the testboard

Roshan Khatri Luitel

Punjab University

SKY130

GitHub

8x PLL Clock Multiplier IP with an input frequency range of 5Mhz to 12.5Mhz and output frequency range of 40Mhz to 100Mhz, giving a 8x multiplied clock at ~50% duty cycle on tt corner at room temperature.

Lakshmi S

Georgia Institute of Technology, USA

SKY130

GitHub

RISCV Developement Board

A Radhika

University of Hyderabad (UOH), Hyderabad

RISC V

GitHub

OpenLANE RTL2GDS for mixed signal SoC (Inputs = mixed signal Verilog, OpenLANE RTL2GDS tools, outputs = GDSII)

Praharsha Mahurkar

Maharashtra Institute of Technology, Pune

SKY130

GitHub

Standard cell characterization flow using ngspice/Magic/OpenLANE

Nickson Jose

VSD Intern

SKY130

GitHub

Euler’s path generation

Open-source Layout Generator (Inputs = Digital or Analog Circuit, Output = Layout)

Sethupathi Balakrishnan

VSD Intern

OSU180

GitHub

SRAM (4kB) using OpenRAM

SRAM (1024 x 32): (32kbits or 4kB), 1.8V and access time is <2.5ns (OpenRAM)

Yash Kumar

Fr. Conceicao Rodrigues College of Engineering, Mumbai

OSU180

GitHub

SRAM (4kB) using OpenRAM

SRAM (1024 x 32): (32kbits or 4kB), 1.8V and access time is <2.5ns (OpenRAM)

Reuel Reuben

BVPCOE, Mumbai

OSU180

GitHub

SRAM (4kB) using OpenRAM

SRAM (1024 x 32): (32kbits or 4kB), 1.8V and access time is <2.5ns (OpenRAM)

Penumarthi Aishwarya

NIT Jamshedpur

OSU180

GitHub

On-chip 8x clock multiplier

On-chip Clock multiplier (pll) (Fclkin – 5MHz to 12Mhz, Fclkout – 40MHz to 100MHz at 1.8v

Paras Sanjay Gidd

Manipal Institute of Technology, (MAHE)

OSU180

GitHub

On-chip 8x clock multiplier

On-chip Clock multiplier (pll) (Fclkin – 5MHz to 12Mhz, Fclkout – 40MHz to 100MHz at 1.8v

Abel Joseph John

NSS College of Engineering, Palakkad

GitHub

10-bit DAC

10bit potentiometric DAC 3.3v analog voltage, 1.8v digital voltage and 1 off-chip external voltage reference

Ashutosh Sharma

IIITD&M Kurnool

OSU180

GitHub

10-bit DAC

10bit potentiometric DAC 3.3v analog voltage, 1.8v digital voltage and 1 off-chip external voltage reference

Neethu Johny

B.M.S College of Engineering, Bangalore

GitHub

10-bit ADC

10-bit ADC 3.3v analog voltage, 1.8v digital voltage and 1 off-chip external voltage reference

Sheryl Corina Serrao

Fr. Conceicao Rodrigues College of Engineering, Mumbai

V.Uday

Siddhartha Institute of Technology

Shalini Priya

NIT Jamshedpur

OSU180

GitHub

10-bit ADC

Comparator part of ADC

Ananya Ghorai

IIT(ISM) Dhanbad

OSU180

GitHub

General purpose band-gap reference with N-well resistors at VDD=3.3v, Vbgp=1.2v

Ankur Sah

National Institute of Technology, Jamshedpur

OSU180

GitHub

6T-SRAM cell

Anusha R

Visveswaraya Technological University (VTU)

OSU180

GitHub

10bit potentiometric DAC 3.3v analog voltage, 1.8v digital voltage and 1 off-chip external voltage reference@osu180nm

Bellana Avinash Naidu

National Institute of Technology, Rourkela

OSU180

GitHub

Open-source Power analysis tool – average switching power and leakage power using Python engine

Charu Gupta

DTU, Delhi

OSU180

GitHub

10bit potentiometric DAC 3.3v analog voltage, 1.8v digital voltage and 1 off-chip external voltage reference@osu180nm

Jayasri Veeravilli

SRM University

OSU180

GitHub

Bi-directional Buffer with Non-Inverting CMOS Input and Gated Pull-down and Pull-up

Nalla Gowthami

National Institute of Technology Rourkela

OSU180

GitHub

10bit potentiometric DAC 3.3v analog voltage, 1.8v digital voltage and 1 off-chip external voltage reference@osu180nm

Neelam Buddhiram Chaurasiya

Mumbai University

OSU180

GitHub

4-input &2-input, 1-output 3.3V analog multiplexer with 1.8V digital select line@osu180nm

Prithivi Raj K

National Institute Of Technology, Tiruchirapalli

OSU180

GitHub1

GitHub2

General purpose band-gap reference with N-well resistors at VDD=3.3v, Vbgp=1.2v

Sheryl Corina Serrao

Mumbai University

OSU180

GitHub

Bi-directional Buffer with Non-Inverting CMOS Input and Gated Pull-down and Pull-up

Tanvi Arora

Deenbandhu Chhotu Ram University of Science and Technology, Murthal, Sonipat

OSU180

GitHub

Open-source Power analysis tool – average switching power and leakage power using TCL engine

Yalamanchili Vahini

NIT Jamshedpur

OSU180

GitHub

VSD, standing as a trailblazing Semiconductor EdTech company and a community-based Technology Aggregator, is revolutionizing the landscape of VLSI Design. With the belief that “Creativity is just connecting things”, VSD has mastered the art of linking the right resources with the community. This unique approach has sparked a significant transformation in the VLSI Design process.

Over the past decade, VSD has made remarkable strides in the open-source semiconductor domain. Our journey includes the development of comprehensive training content, empowering students to design silicon-grade IP/SoC. Notably, we’ve successfully guided these projects through the tapeout cycle via the Google open shuttle program. This achievement is a testament to our commitment to hands-on, practical education.

At VSD, our role extends beyond traditional education. While we didn’t invent EDA tools or design flows, we’ve made them accessible to a wider community. Our mentorship has been instrumental in the development of over 50+ Analog/Digital IPs and solutions. Impressively, 20+ of these have successfully transitioned from concept to Silicon – a clear indicator of our effective approach and the high quality of work produced under our guidance.

We pride ourselves on fostering a community-based revolution in the Semiconductor Industry. By democratizing access to advanced tools and knowledge, VSD is not just educating individuals; we are building a community of innovators poised to lead the next wave of advancements in the semiconductor sector. With VSD, the future of VLSI Design is not just being written; it’s being rewritten by a passionate and empowered community.

VSDSquadron was launched by Prof. V. Kamakoti, Director of IIT Madras

VSD Launches VSDSquadron In Collaboration With IIT Madras & DIR-V

Job Roles, Convergence With Embedded Systems, and Startups

VSD showcased at Semicon India 2023

VSDSquadron Educational board on Tamil News channel

5 Day Workshop on VLSI Design Flow using RISCV and EDA Tools

Karnataka VLSI roadshow at Sahyadri College, Mangalore

Welcome to Ethical RISC-V IoT Workshop

The “Ethical RISC-V IoT Workshop” at IIIT Bangalore, organized in collaboration with VSD, is a structured, educational competition aimed at exploring real-world challenges in IoT and embedded systems. Participants progress through three stages: building an application, injecting and managing faults, and enhancing application security. The event spans from May 9 to June 15, 2024, culminating in a showcase of top innovations and an award ceremony. This hands-on hackathon emphasizes learning, testing, and securing applications in a collaborative and competitive environment.

VSDSquadron, a cutting-edge development board based on the RISC-V architecture that is fully open-source. This board presents an exceptional opportunity for individuals to learn about RISC-V and VLSI chip design utilizing only open-source tools, starting from the RTL and extending all the way to the GDSII. The possibilities for learning and advancement with this technology are limitless.

Furthermore, the RISC-V chips on these boards should be open for VLSI chip design learning, allowing you to explore PNR, standard cells, and layout design. And guess what? vsdsquadron is the perfect solution for all your needs! With its comprehensive documentation and scalable labs, thousands of students can learn and grow together.

With VSD Hardware Design Program (VSD-HDP), you have the opportunity to push the boundaries of what exist in open source and establish the new benchmark for tomorrow.

It will leverage your degree in Electrical or Computer Engineering to work with

Sounds exciting to just get started with expert mentors, doesn’t it? But we are looking for the next generation of learners, inventors, rebels, risk takers, and pioneers.

“Spend your summer working in the future !!”

Outcomes of VSD Online Research IP Design Internship Program

VSD – Intelligent Assessment Technology (VSD-IAT) is expertly built training platform and is suited for designer requirements. Semiconductor companies understand the value of training automation and Engineer performance enhancement, and do not need to be convinced of the impact of a virtual platform for learning. VSD trainings are quick, relevant, and easy to access from any device at any time zone.

VSD is working towards creating innovative talent pool who are ready to develop design and products for the new tech world. VSD believes in “Learning by doing principle” , and always prepare the student to apply the knowledge learned in the workshops, webinars and courses. We always push our students to work on new designs, test it and work continuously till it becomes the best performing design. Any student who enrolls to VSD community starts working with small design and grows with us and develops a tapeout level design with complete honesty and dedication towards the Work !!

Check out VSD Interns Achievement!

Welcome to the World’s only online conference in Semiconductor Industry VSDOpen Conference. With enormous support and global presence of audience from different segments of industrial lobby and academia made a highly successful event. Evolution is change in the genetic makeup of a population over time, online conference is one kind evaluation everyone adapt soon.

VSD offers online course in complete spectrum of vlsi backend flow from RTL design, synthesis and Verification, SoC planning and design, Sign-off analysis, IP Design, CAD/EDA automation and basic UNIX/IT, Introduction to latest technology – RISC-V, Machine intelligence in EDA/CAD, VLSI Interview FAQ’s.

Current Reach – As of 2021, VSD and its partners have released 41 online VLSI courses and was successfully able to teach ~35900 Unique students around 151 countries in 47 different languages, through its unique info-graphical and technology mediated learning methods.