VSDSquadron RTL-to-GDS “6-weeks” Program is a structured, hands-on journey that trains participants to think and work like real silicon engineers — from system-level RTL all the way to a manufacturable chip layout.

This program goes beyond isolated labs or tool demos. Participants work with a realistic SoC-level reference architecture, follow industry-style hierarchical design practices, and experience the complete lifecycle of a chip: functional verification, physical implementation, timing closure, and final assembly — all using open-source EDA tools.

At the heart of the program is a Caravel-based management SoC architecture, adapted for education and extended to support a hierarchical RTL-to-GDS flow. The user project area is intentionally disabled, allowing participants to focus on core SoC building blocks, system integration, and physical design fundamentals without the noise of pad-level or shuttle-specific complexity.

Participants progressively build expertise across three critical dimensions of chip design:

This mirrors how real silicon teams work — with ownership at block level, clean interfaces, and staged sign-off.

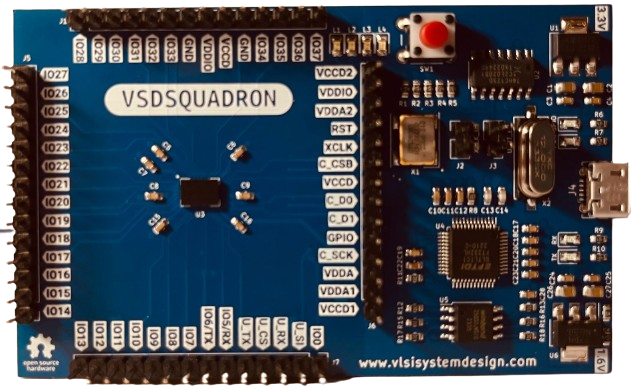

An educational kit and cutting-edge development board. With general-purpose interfaces that enables to evaluate features of RISC-V ISA

An exceptional opportunity for individuals to learn about RISC-V and VLSI chip design utilizing only open-source tools.

VSDSquadron labs are designed to get started with RISC-V programming, synthesis, physical design, and circuit design.

Kit includes RISC-V Programming and VLSI Chip Design industry grade educational content.

The VSDSquadron board comes with a minimum of 10 GPIOs, which makes it ideal for a diverse range of projects.

VSDSquadron Modules covers RISC-V Basics, RTL Design and Synthesis, Physical Design, Circuit design and SPICE simulations.

SCL180 PDK + OpenROAD — used to demonstrate hierarchical design, block reuse, and realistic backend constraints.

Sky130 PDK + OpenROAD — participants who do not have access to SCL PDKs can fully participate using Sky130 without losing learning value

Full-chip functional simulation and verification (RTL-level, system bring-up using open-source simulators)

Block-level physical design (OpenROAD-based synthesis, placement, routing, STA, and DRC/LVS)

Gate-level functional verification (Simulation using timing-aware, post-layout netlists)

Full-chip assembly and tapeout-ready integration (Hierarchical assembly using timing-closed blocks and macros)

VSD, standing as a trailblazing Semiconductor EdTech company and a community-based Technology Aggregator, is revolutionizing the landscape of VLSI Design. With the belief that “Creativity is just connecting things”, VSD has mastered the art of linking the right resources with the community. This unique approach has sparked a significant transformation in the VLSI Design process.

Over the past decade, VSD has made remarkable strides in the open-source semiconductor domain. Our journey includes the development of comprehensive training content, empowering students to design silicon-grade IP/SoC. Notably, we’ve successfully guided these projects through the tapeout cycle via the Google open shuttle program. This achievement is a testament to our commitment to hands-on, practical education.

At VSD, our role extends beyond traditional education. While we didn’t invent EDA tools or design flows, we’ve made them accessible to a wider community. Our mentorship has been instrumental in the development of over 50+ Analog/Digital IPs and solutions. Impressively, 20+ of these have successfully transitioned from concept to Silicon – a clear indicator of our effective approach and the high quality of work produced under our guidance.

We pride ourselves on fostering a community-based revolution in the Semiconductor Industry. By democratizing access to advanced tools and knowledge, VSD is not just educating individuals; we are building a community of innovators poised to lead the next wave of advancements in the semiconductor sector. With VSD, the future of VLSI Design is not just being written; it’s being rewritten by a passionate and empowered community.

(18 % GST applicable and FREE Shipping)

Also available on

RISC-V and VLSI Educational Board

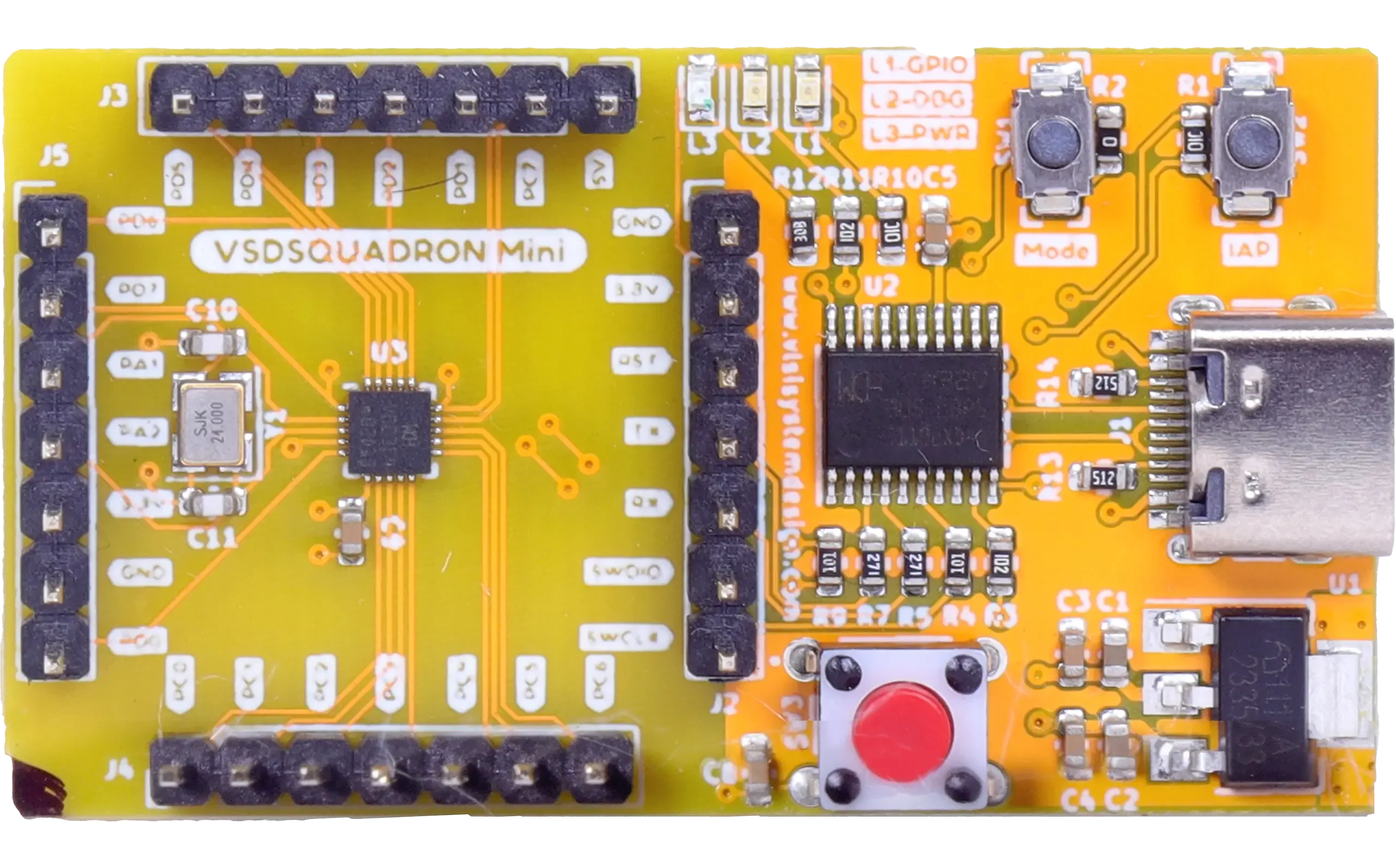

CH32 RISC-V

Lower Power Embedded Board enabling Edge RISC-V Product Development

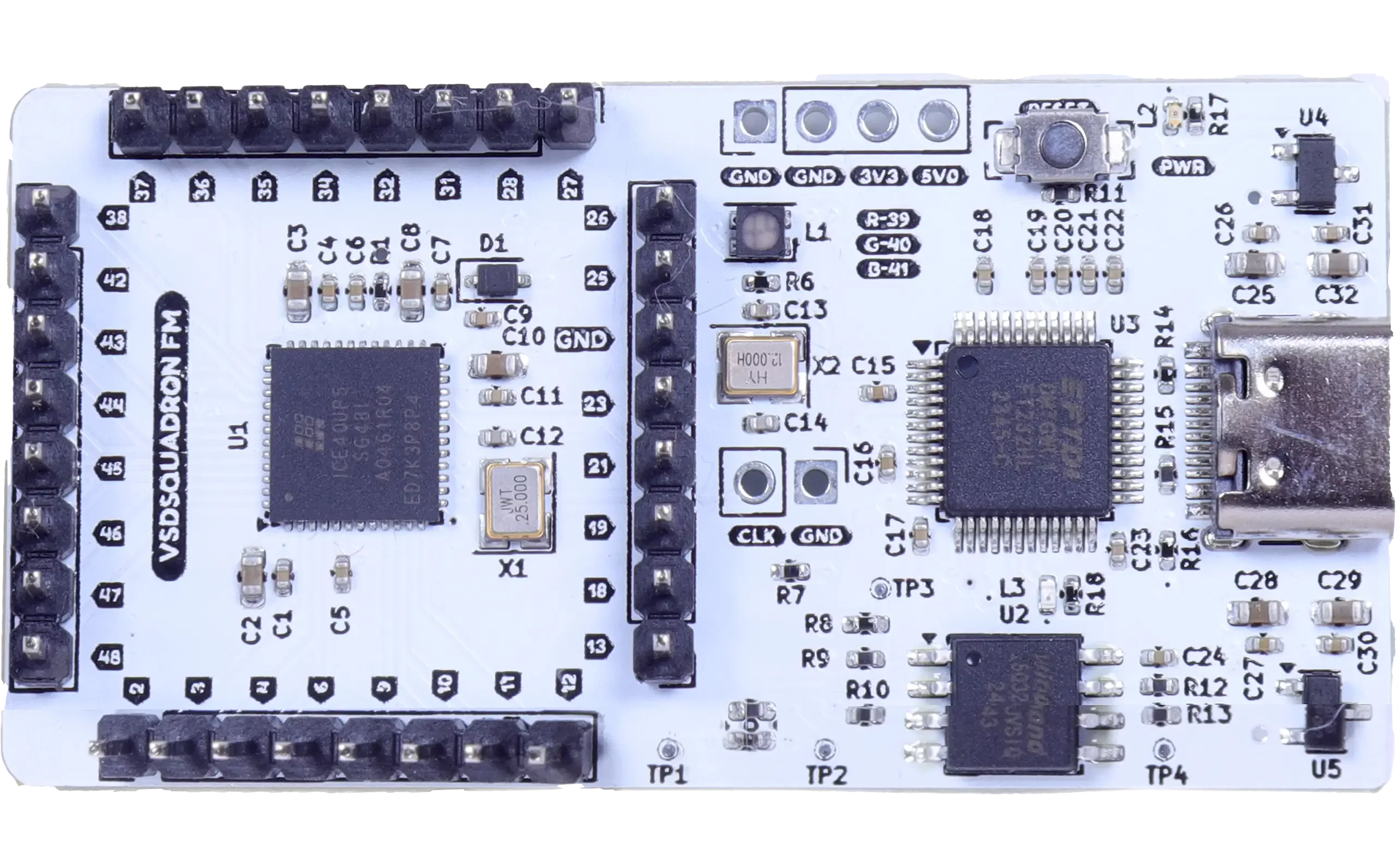

ICE40UP5K

Easy to use FPGA Board with high LUT count for rapid prototyping

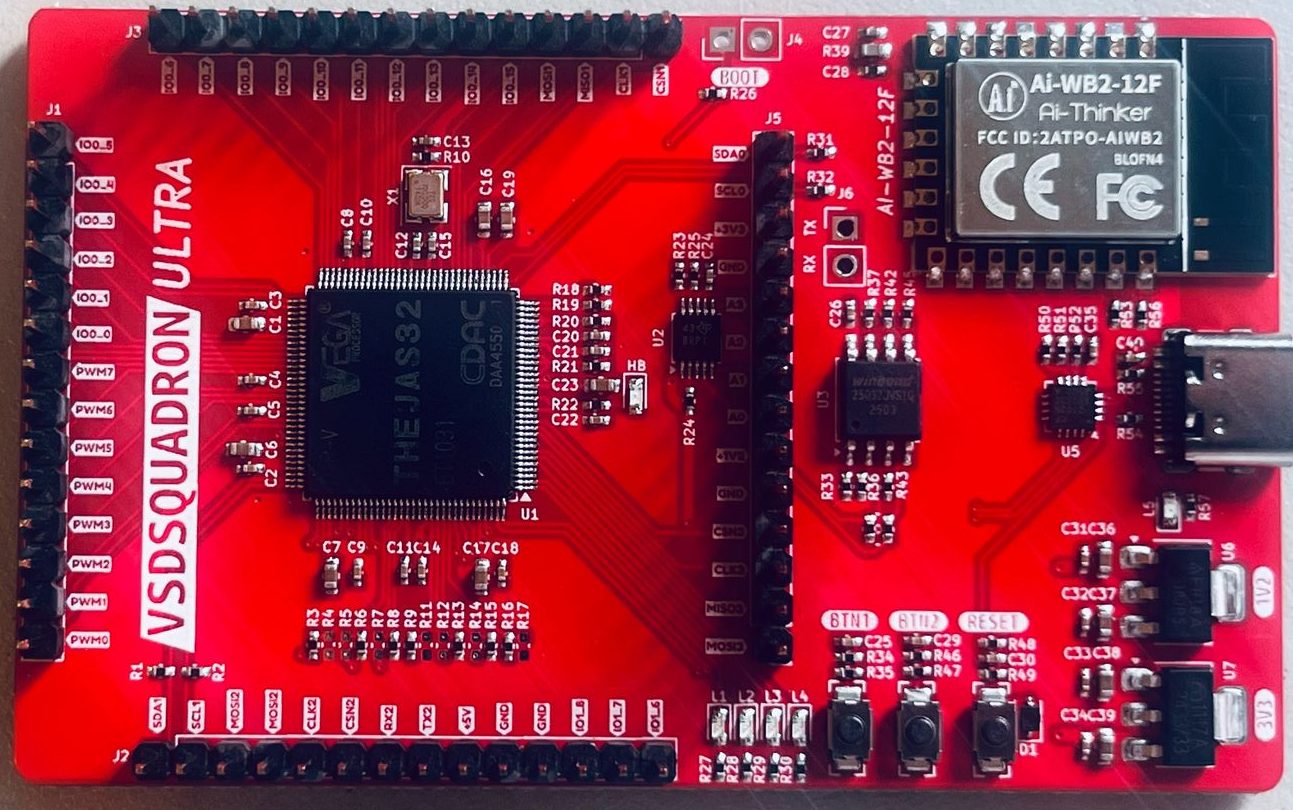

THEJAS32 SoC

RISC-V Development Board powered by C-DAC’s VEGA Processor.

VSD, standing as a trailblazing Semiconductor EdTech company and a community-based Technology Aggregator, is revolutionizing the landscape of VLSI Design. With the belief that “Creativity is just connecting things”, VSD has mastered the art of linking the right resources with the community. This unique approach has sparked a significant transformation in the VLSI Design process.

Over the past decade, VSD has made remarkable strides in the open-source semiconductor domain. Our journey includes the development of comprehensive training content, empowering students to design silicon-grade IP/SoC. Notably, we’ve successfully guided these projects through the tapeout cycle via the Google open shuttle program. This achievement is a testament to our commitment to hands-on, practical education.

At VSD, our role extends beyond traditional education. While we didn’t invent EDA tools or design flows, we’ve made them accessible to a wider community. Our mentorship has been instrumental in the development of over 50+ Analog/Digital IPs and solutions. Impressively, 20+ of these have successfully transitioned from concept to Silicon – a clear indicator of our effective approach and the high quality of work produced under our guidance.

We pride ourselves on fostering a community-based revolution in the Semiconductor Industry. By democratizing access to advanced tools and knowledge, VSD is not just educating individuals; we are building a community of innovators poised to lead the next wave of advancements in the semiconductor sector. With VSD, the future of VLSI Design is not just being written; it’s being rewritten by a passionate and empowered community.

VSDSquadron was launched by Prof. V. Kamakoti, Director of IIT Madras

VSD Launches VSDSquadron In Collaboration With IIT Madras & DIR-V

Job Roles, Convergence With Embedded Systems, and Startups

VSD showcased at Semicon India 2023

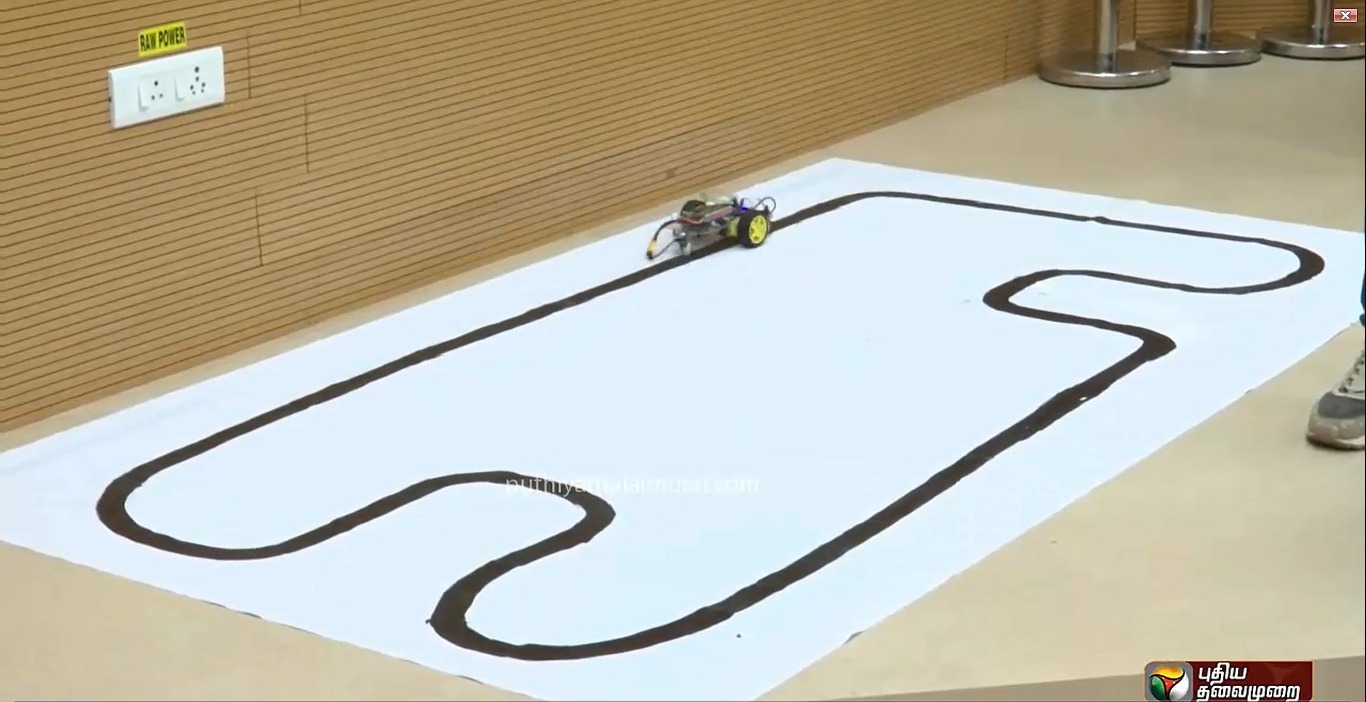

VSDSquadron Educational board on Tamil News channel

5 Day Workshop on VLSI Design Flow using RISCV and EDA Tools

Karnataka VLSI roadshow at Sahyadri College, Mangalore

Welcome to Ethical RISC-V IoT Workshop

The “Ethical RISC-V IoT Workshop” at IIIT Bangalore, organized in collaboration with VSD, is a structured, educational competition aimed at exploring real-world challenges in IoT and embedded systems. Participants progress through three stages: building an application, injecting and managing faults, and enhancing application security. The event spans from May 9 to June 15, 2024, culminating in a showcase of top innovations and an award ceremony. This hands-on hackathon emphasizes learning, testing, and securing applications in a collaborative and competitive environment.

VSDSquadron, a cutting-edge development board based on the RISC-V architecture that is fully open-source. This board presents an exceptional opportunity for individuals to learn about RISC-V and VLSI chip design utilizing only open-source tools, starting from the RTL and extending all the way to the GDSII. The possibilities for learning and advancement with this technology are limitless.

Furthermore, the RISC-V chips on these boards should be open for VLSI chip design learning, allowing you to explore PNR, standard cells, and layout design. And guess what? vsdsquadron is the perfect solution for all your needs! With its comprehensive documentation and scalable labs, thousands of students can learn and grow together.

With VSD Hardware Design Program (VSD-HDP), you have the opportunity to push the boundaries of what exist in open source and establish the new benchmark for tomorrow.

It will leverage your degree in Electrical or Computer Engineering to work with

Sounds exciting to just get started with expert mentors, doesn’t it? But we are looking for the next generation of learners, inventors, rebels, risk takers, and pioneers.

“Spend your summer working in the future !!”

Outcomes of VSD Online Research IP Design Internship Program

VSD – Intelligent Assessment Technology (VSD-IAT) is expertly built training platform and is suited for designer requirements. Semiconductor companies understand the value of training automation and Engineer performance enhancement, and do not need to be convinced of the impact of a virtual platform for learning. VSD trainings are quick, relevant, and easy to access from any device at any time zone.

VSD is working towards creating innovative talent pool who are ready to develop design and products for the new tech world. VSD believes in “Learning by doing principle” , and always prepare the student to apply the knowledge learned in the workshops, webinars and courses. We always push our students to work on new designs, test it and work continuously till it becomes the best performing design. Any student who enrolls to VSD community starts working with small design and grows with us and develops a tapeout level design with complete honesty and dedication towards the Work !!

Check out VSD Interns Achievement!

Welcome to the World’s only online conference in Semiconductor Industry VSDOpen Conference. With enormous support and global presence of audience from different segments of industrial lobby and academia made a highly successful event. Evolution is change in the genetic makeup of a population over time, online conference is one kind evaluation everyone adapt soon.

VSD offers online course in complete spectrum of vlsi backend flow from RTL design, synthesis and Verification, SoC planning and design, Sign-off analysis, IP Design, CAD/EDA automation and basic UNIX/IT, Introduction to latest technology – RISC-V, Machine intelligence in EDA/CAD, VLSI Interview FAQ’s.

Current Reach – As of 2021, VSD and its partners have released 41 online VLSI courses and was successfully able to teach ~35900 Unique students around 151 countries in 47 different languages, through its unique info-graphical and technology mediated learning methods.