Hi There,

The task given to me was “Design of Open-source Power analysis tool – calculate average switching power and leakage power – Using TCL/Perl/Python – any language”. The entire program is divided into 4 phases.

Phase I:

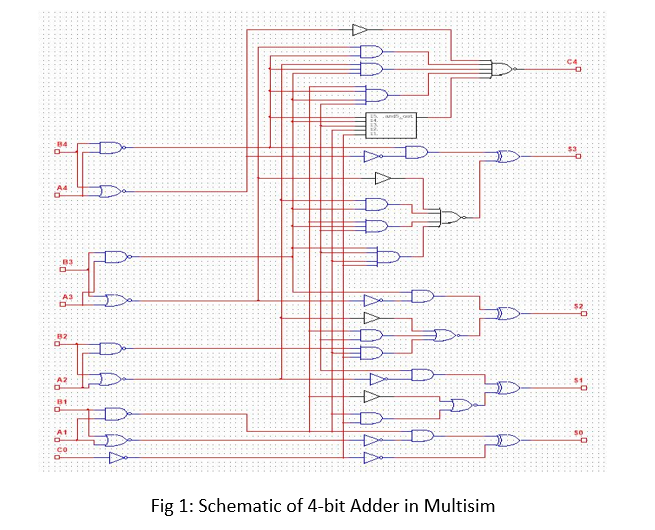

In first 3 weeks, we need to find out three essential things: “What to do?”, “Why to do?” and “How to do?”. During this phase, A brief analysis on power, its classification and importance of power tools in VLSI industry is done. The application circuits such as 4-bit adder, ALU are designed in NI Multisim and later in LTSpice using osu018 pdks.

Phase II:

In this phase, the methodology of the power tool was proposed. I chose TCL language to code as it is somewhat similar to C++. A basic code from scrap is built at first. The inputs taken for this code are supply voltage (VDD), load capacitance (CL), switching frequency (f) used in circuit and it gives the calculated switching power value. The equation used for calculating switching power is

P_dynamic = 1/2 CL * Vdd^2 * F

The main challenge for me in this phase is coding in TCL language which is completely unknown to me. I have to learn it and write the code to calculate the required power values.

Phase III:

After Phase II evaluation, feedback from Kunal Ghosh helped to build up this power tool. Later, the basic idea to find average switching power and leakage power from ngspice netlist is given by Prof. Sudhakar Mande from Don Bosco Institute of Technology, Mumbai. The idea is taken from textbook CMOS digital Integrated circuits by Kang.

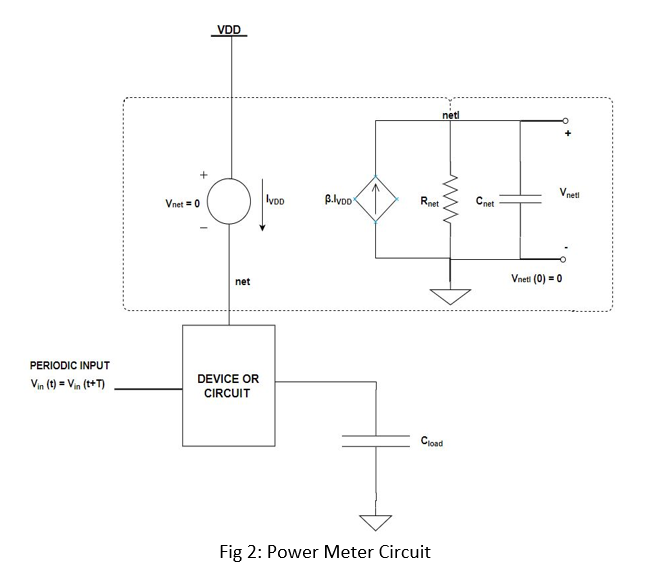

A separate power meter is built which gives the average power of the circuit. The integral of instantaneous supply voltage VDD and the current drawn from power meter shown in fig2 over a period for a periodic input gives the average switching power of entire circuit which acts as sub circuit in power meter. The mathematical approach is clearly given in the textbook CMOS digital Integrated circuits by Kang.

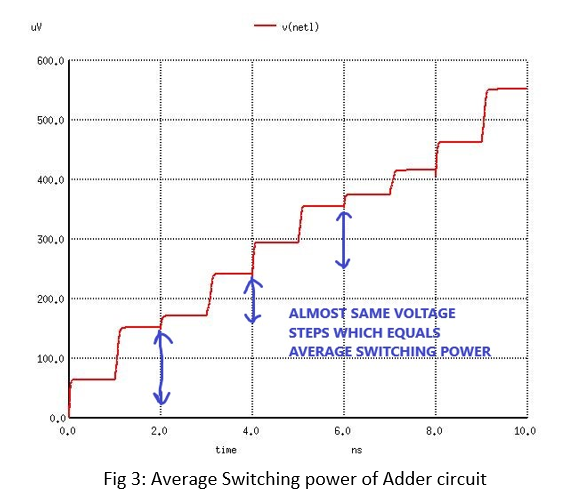

As shown in fig3, the measured step difference in voltage across power meter over a constant time period (here 2ns) is equivalent to the average switching power. For this a new netlist is written by modifying the user given netlist.

As shown in fig3, the measured step difference in voltage across power meter over a constant time period (here 2ns) is equivalent to the average switching power. For this a new netlist is written by modifying the user given netlist.

The leakage power is calculated by using operating point (.op) analysis used in ngspice with little modifications in the user given netlist.

Phase IV:

Till phase III, manual writing is done for modification of netlists. This phase is quite challenging as it involves the automating the modifications using TCL shell scripting. At first individual codes are written for calculating switching power and leakage power, later both codes were merged.

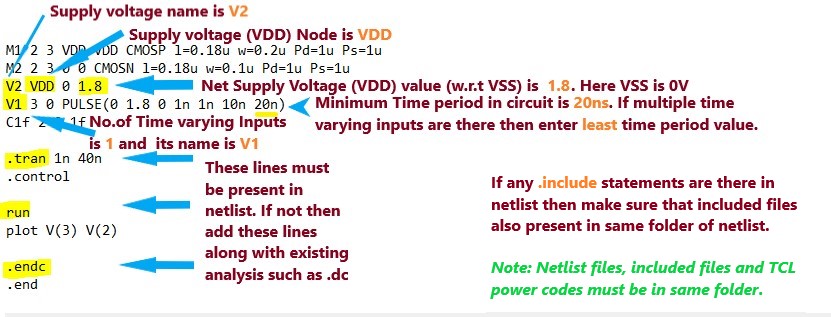

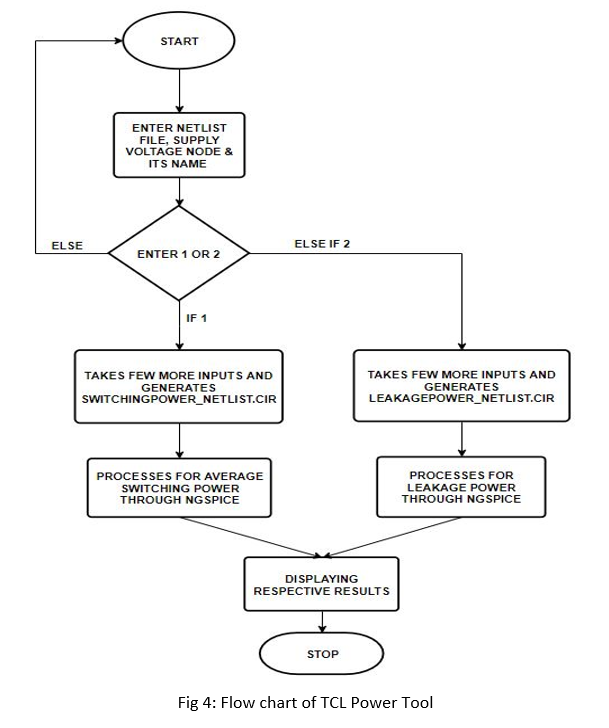

Fewer inputs from user that related to netlist were taken such as supply node name, supply voltage value were taken to modify the user given netlist and forms new netlist. Now the new netlists are inputs to power tool. The calculation of average switching power and leakage power is done using tcl code after obtaining the data from running the new netlists using ngspice. A flow diagram is shown in fig4 for better understanding of power tool.

At this point, it seems that main goal is achieved but there is some manual operation such as running ngspice. I felt to automate this thing. Here the shell commands of TCL and great support from Philipp Gühring helped in achieving this idea

To check the compatibility of designed power tool, we took circuit netlists of other interns and calculated the power values. Even individual power tools are also checked for the compatibility.

Limitations:

Since the foundation tool for the designed power analysis tool is ngspice, the user netlist has to be compatible with the Ngspice tool.

Despite challenges and fear, we completed the 8-week internship successfully but there is a lot more work to do!

For detailed source code and flow, refer the github repo: vsdtclpowertool.

Refer below link to know more about VSD-IAT workshops and future internships:

https://www.vlsisystemdesign.com/vsd-iat/

Related Posts:

- Bluetooth automated smart access

- Accelerating the Future of Semiconductor Talent with…

- Water level monitoring and control in water tank

- LiFi Lock - An authentication system using LiFi…

- Home safety system

- 40 Basic Questions to Prepare in Combinational Circuits

- RISC-V Mini Game Console

- The Future of Chip Design: The Next Generation is…

- Smart Plant Care using the VSD_Squadron-MINI-BOARD

- Real Time Implementation of BitNetMCU