What I did in 8-weeks-VSD Internship? On-chip PLL using Sky130

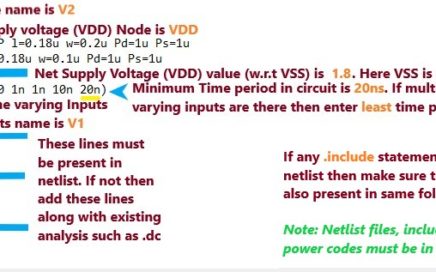

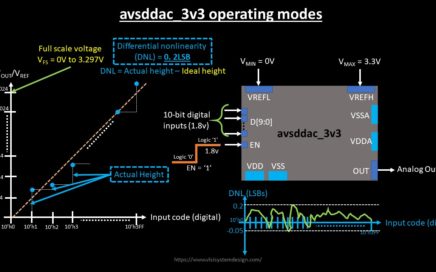

In this 8-week internship I spent the first week on researching existing work and making design decisions for the PLL components namely – Phase Frequency Detector, Charge Pump, Voltage Controlled Oscillator and Frequency Divider. I also looked into linking of the Sky130nm PDK with SPICE for the circuit implementation.