Are you ready for Embedded-UVM webinar?

Hey There, Of-course there is a requirement for open-source verification, but that’s not the only thing we want to cater to. There are other verification […]

Hey There, Of-course there is a requirement for open-source verification, but that’s not the only thing we want to cater to. There are other verification […]

Hey There, It’s time – We are looking to talk to our hardware, and we need you in Bangalore (2-3 or 4-6 yrs work ex) […]

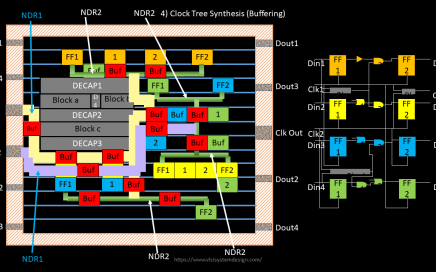

Hey There – Think about it…!! Problem Statement – For hierarchical designs ~500k instance count, participants are expected to develop code which will modify existing […]

Hey There – Think about it!! Today’s version of open-source EDA tools, work very well for hierarchical designs sub-25k instance count. For hierarchical designs ~500k […]

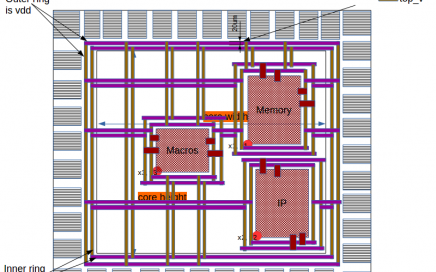

Hey There, Our team worked really hard to get Robot + MP3 player using India’s First Indegenious 32-bit RISC-V Microprocessor “Shakti E-Class”…This one is Shakti […]

Hey There – Think about it!!! Today’s version of open-source EDA tools, work very well for hierarchical designs sub-25k instance count. For hierarchical designs ~500k […]

With learning being online, SHAKTI core and ‘vsdflow’ being opensource, this is first-time in the history of VLSI design & EDA (thanks to RISC-V ecosystem and Shakti Team at IITM lead by Prof. Kamakoti), a chip will ever be taped-out using all open source flow, which will cater to almost 80% Indian Semiconductor Market.