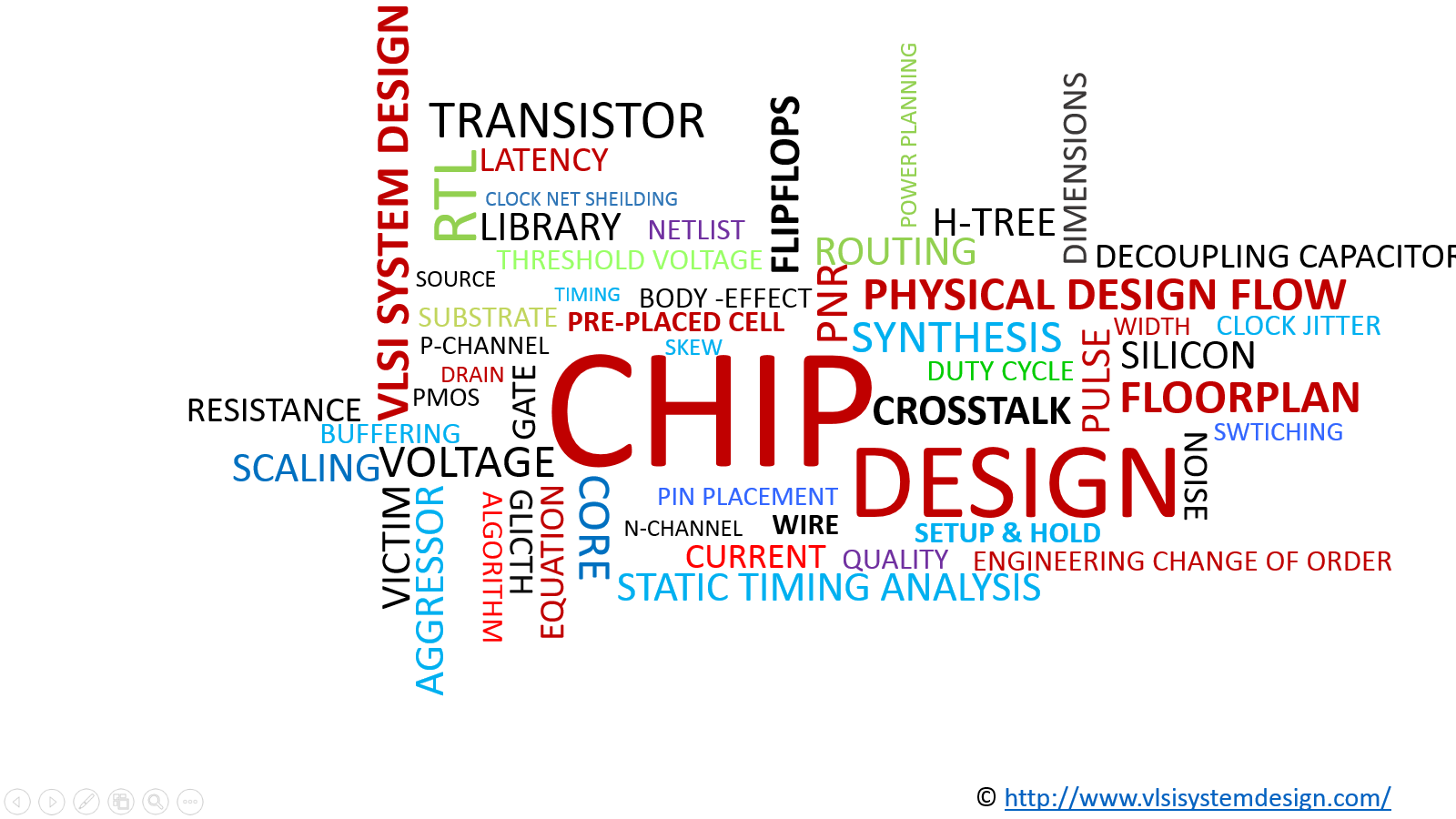

Mixed-signal PNR flow using openlane/sky130nm process

GitHub is the new Resume for VLSI industry

GitHub is the new Resume for VLSI industry

So, I took up two STA tools, OpenSTA from openroad project and “——-” from “——-“, to explain, to some extent, what “bench-marking” means to me. I would also encourage everyone reading this blog to come up with their definitions of “bench-marks” for other tools and we can model that. You can fill-up “——” with one of your favorite industry grade EDA tools. The concept of benchmark won’t change

Online university Course name – Foundation of Computer Systems Design

This course is being taught by Prof. V. Kamakoti, who needs no introduction, who lead India’s first RISC-V microprocessor SHAKTI teamand made all of us proud.

With learning being online, SHAKTI core and ‘vsdflow’ being opensource, this is first-time in the history of VLSI design & EDA (thanks to RISC-V ecosystem and Shakti Team at IITM lead by Prof. Kamakoti), a chip will ever be taped-out using all open source flow, which will cater to almost 80% Indian Semiconductor Market.

Hi Vlsi

Your feedback has been continuously pushing us to the edge. And I really want to Thank You for all the support you have been giving over the past. Its due to this push, we are now releasing (especially for VLSI freshers), a package, which you just need to download/run. That would install all opensource EDA tools on your UNIX machine plus run a complete RTL-2-GDS on RISC-V core ‘picorv32’.

All you need to do is go to below github link, and follow simple 5 steps given in the README of below link:

In last 50 years, there are 3 lessons that we can draw. First – software advances can inspire architecture innovations. Second – when we raise the hardware/software interface, it creates opportunities for architecture innovation. Third – in our field, the way we settle these debates, isn’t by just arguing in a bar, rather people spent/invest billions of dollars to investigate their ideas and marketplace settles these debates

Hi “Pictures speak it all” Finally, we all did it – VSDOpen – first ever online VLSI conference. Very close to a real one – […]

“Design at $0” is an initiative driven by our team at VSD.Working in open environment is much easier process as all the resources are openly available, but here arise the loophole.

Steve Hoover is the founder of Redwood EDA. Steve holds a BS in electrical engineering from Rensselaer Polytechnic Institute and an MS in computer science from the University of Illinois. He has designed numerous components for high-performance server CPUs and network architectures for DEC, Compaq, and Intel. Students will learn Transaction-Level Verilog modelingtechniques to generate Verilog models in half the time using the makerchip.comfree online IDE. A new open-source RISC-V CPU development effort will be introduced that showcases flexible IP design practices.

Mohamed Kassem is the CTO and Co-Founder of efabless.com, the first semiconductor company applying open community innovation to all aspects of product development. Prior to launching efablesshe […]