Hey There – Think about it!!!

Last week, we shared our idea and vision of “How to define the width and height of core and die using opensource EDA tools?” – This is not for toy designs, but for a complex hierarchical designs, with instance count up to 500k instance count

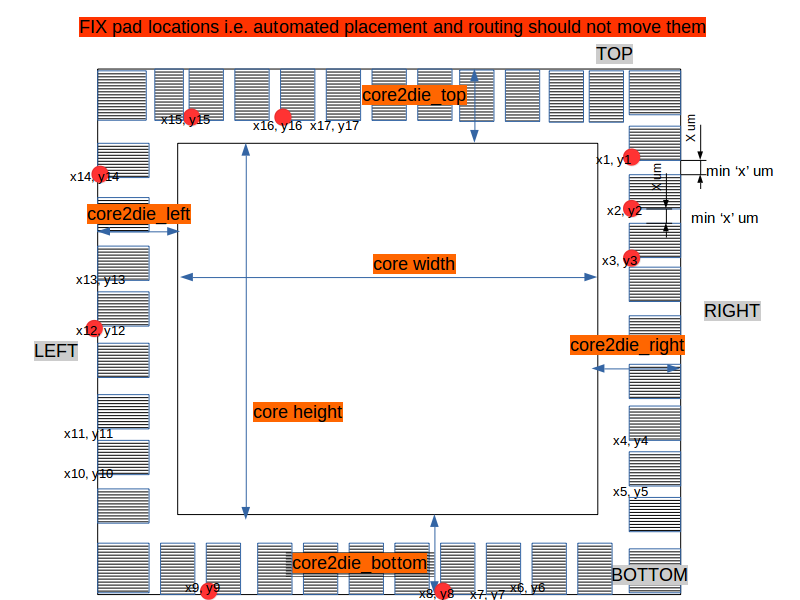

Today’s version of open-source EDA tools, work very well for hierarchical designs sub-25k instance count. For hierarchical designs ~500k instance count, let’s develop code which will enable users to place IO pads and dummy pads, in area between core an die, shown in below image. – Sounds like a very simple problem statement…Believe me, it becomes more tougher, but clearer, the more you think about it

Expected output from this problem statement:

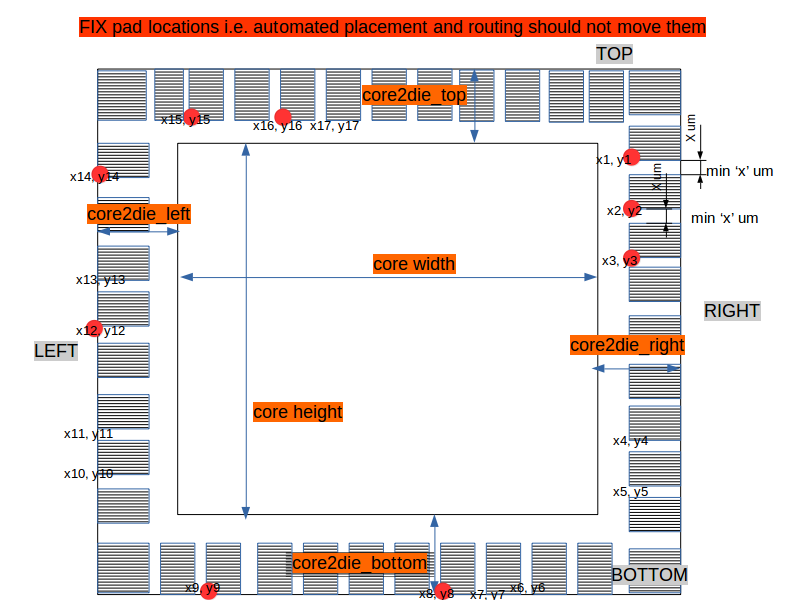

A text file in standard DEF format which has all information about inputs which will be provided, like standard cells PDK’s + synthesized verilog + core/die width and height information and output information about all pad locations (shown in below image)

Let me help you with some steps to implement the above

Step 1) Find a way to parse input DEF file, which has locations, co-ordinates, instance names and many more information of all instances that you see in below image. It can be a command something like below

read_def <input_def_file>

If the DEF file syntax is not in par with standard DEF syntax, issue an error message specifying line number where there is a syntax error

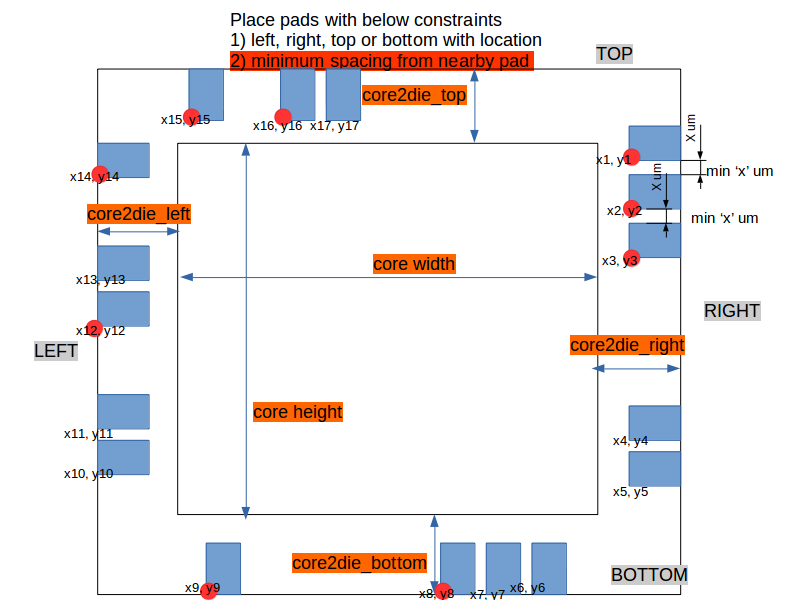

Step 2) Develop code (or command) to place pads (from IO libraries which we will be providing) with below constraints

- Side (left, right, top, bottom)

- X, Y Locations

- minimum spacing with nearby pads

It can be a command something like below

place_pads -pad <pad_instance_name> -preferred_side <left/right/top/bottom/corner> -pad_location <first_half_of_preferred_side_or_second_half_of_preferred_side> -min_spacing_from_left_pad <number_in_um> -min_spacing_from_right_pad <number_in_um>

User will use the above command for all pads. (come up with a strategy to define “corner”)

place_pads -pad pad1 -preferred_side right -pad_location first_half -min_spacing_from_left_pad 25 -min_spacing_from_right_pad 25

place_pads -pad pad2 -preferred_side bottom -pad_location second_half -min_spacing_from_left_pad 25 -min_spacing_from_right_pad 25

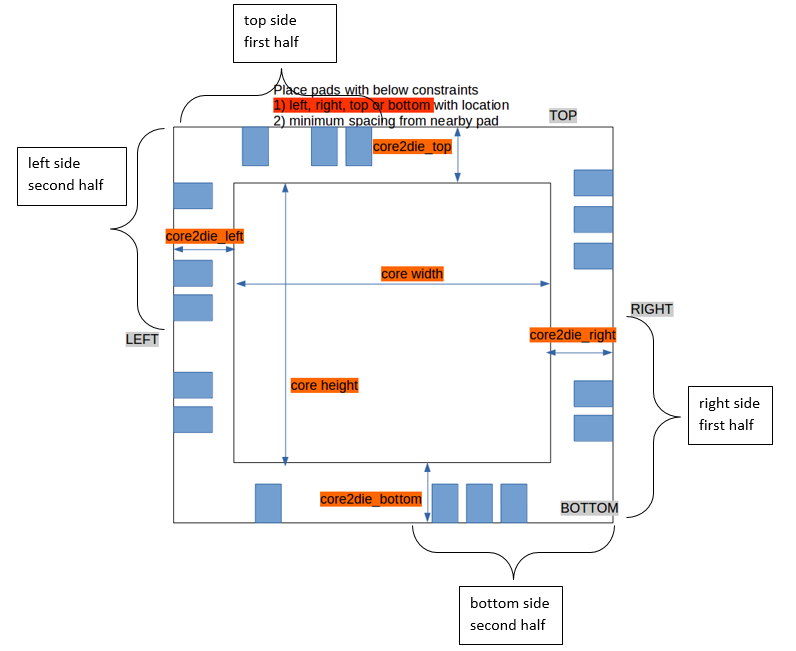

Below image shows what does “right side first half” and “bottom side second half” mean.

This way we can configure and place all pads. Refer to Tim Edward’s placement tool “graywolf”

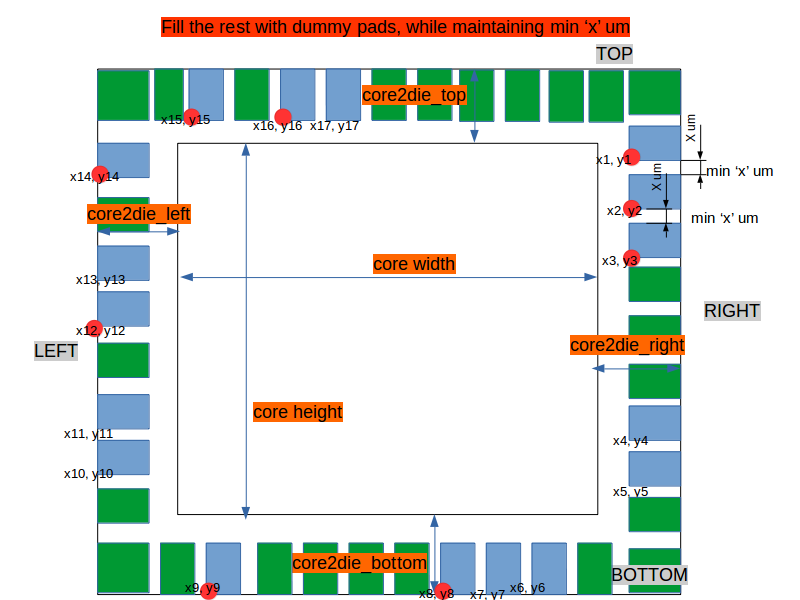

Step 3) Fill the rest area with dummy pads, while maintaining min ‘X’ um. (this means you need to create a dummy pad with available pad as reference)

It can be a command something like below

create_dummy_pad <pad_name> -reference_pad_cell <reference_library_pad_cell_name> -count <number_of_pads_user_wants_to_create> OR

create_dummy_pad <pad_name> -pad_width <number_in_um> -pad_height <number_in_um> -count <number_of_pads_user_wants_to_create>

This will create a dummy pad with the name “pad_name_1”, “pad_name_2”, “pad_name_3” and so on using one reference pad cell which is available in library

place_pads -pad <pad_instance_name> -preferred_side <left/right/top/bottom/corner> -pad_location <first_half_of_preferred_side_or_second_half_of_preferred_side> -min_spacing_from_left_pad <number_in_um> -min_spacing_from_right_pad <number_in_um>

The above command is what we have created in step 2). This will place pads having instance names as “pad_instance_name” as shown below.

User can use the command like below. If square shape pad not available, create dummy square shape pad using -pad_height and -pad_width options given in above “create_dummy_pad” command

create_dummy_pad corner_pad -pad_width 40 -pad_height 40 -count 4

create_dummy_pad normal_pad -reference_pad_cell lib_pad_cell_with_rectangle_shape -count 20

place_pads -pad corner_pad_1 -preferred_side corner

place_pads -pad normal_pad_1 -preferred_side right -pad_location first_half -min_spacing_from_left_pad 25 -min_spacing_from_right_pad 25

place_pads -pad normal_pad_2 -preferred_side left -pad_location second_half -min_spacing_from_left_pad 25 -min_spacing_from_right_pad 25

Step 4) Fix pad locations using standard DEF syntax (+FIXED) which will make sure that any automated placement and routing tool don’t move it

It can be a command something like below

select_cell <list_of_pads> -fixed <true/false>

Terms and condition:

- You are free to use the source code of existing (and only) opensource tools like magic, qflow, graywolf, qrouter.

- Each line of your code needs to be open-sourced and documented

Doesn’t that sound exciting?

Stay tuned below for more….