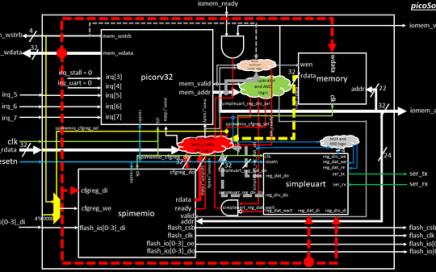

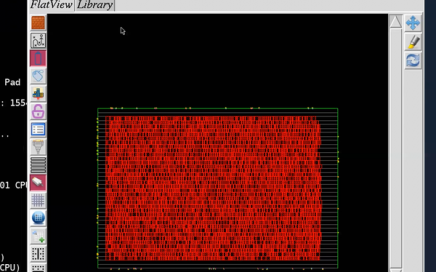

8th mile-stone – A story of 2kbps line and 8x clock multiplier

VSD Research IP design 8-week internship were a series of stories about people and students reaching great heights, using available resources. Thanks to Pandemic, every VSD student from every corner of the world realized the power of open-source EDA for VLSI learning/trainings.