This time, VSD Research IP design 8-week internship were a series of stories about people and students reaching great heights, using available resources. Thanks to Pandemic, every VSD student from every corner of the world realized the power of open-source EDA for VLSI learning/trainings.

Leaving politics aside, imagine what a student would had done in lock-down for past 4-months, has no access to college, hence no access to tool licenses and min internet speed. Thanks to open-source EDA, in last 4 months. Paras Gidd was able to achieve 40MHz to 100MHz clock frequency in PLL mode post-layout using osu180nm tech node in a matter of 8-weeks.

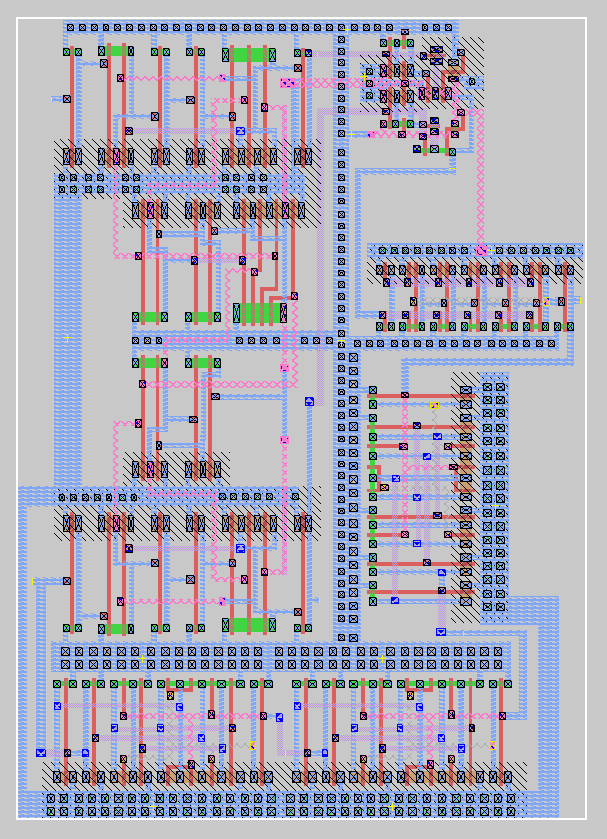

Here’s his entire GitHub repository which explains all minute details about his work – An absolute masterpiece