This blog is regarding abstract submission for VSDOpen2018, which is the first online conference in VLSI, that covers all aspects of semiconductor technology with prime focus to build SoC using RISC-V CPU by illustrating exciting ways using (only) opensource EDA tools.

This conference has 6 symposium, out of which first symposia is to come up with front-end EDA tool flows for IC design and verification. List of other symposium and session chair can be found in below link:

https://www.vlsisystemdesign.com/vsdopen2018-2/

This blog is about Symposium I – Front-end open-source EDA tool flows for IC design and verification (abstract submission last date is 15th August, please see above link for details)

Let’s see how you can implement a pipe-line in transaction-level verilog using Makerchip IDE, which is primarily the mode of implementation for this Symposium

Pipeline:

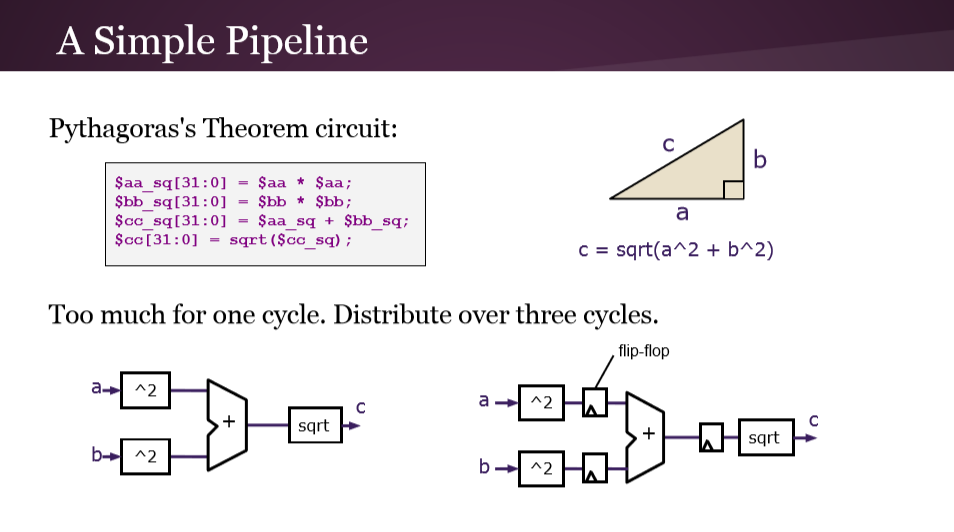

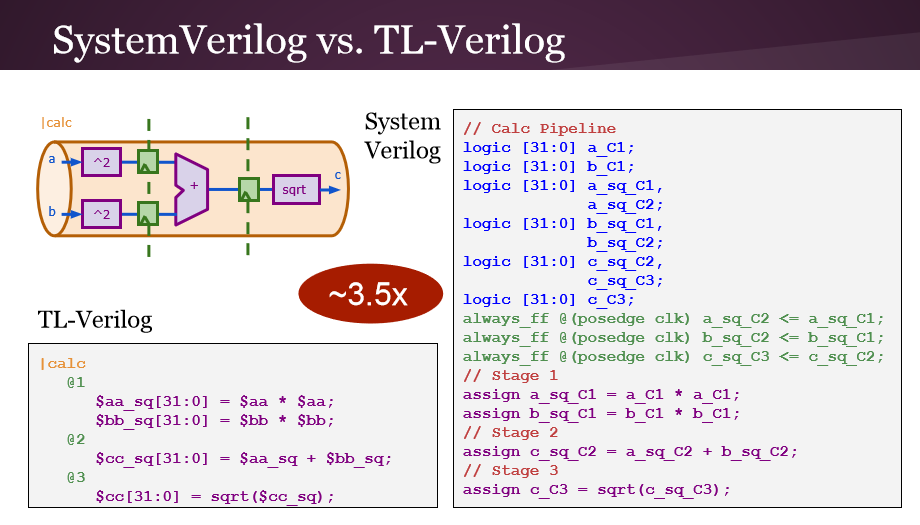

Pipeline is analogous to assembly plant, where we divide the processing work into stages, as you saw with RISC-V micro architecture (read this blog for more details). Let’s take an example of a logic which is computing Pythagoras theorem. The below code is the logic that is computing Pythagoras’s theorem. It’s computing the distance ‘c’ as square root of (a^2 + b^2)

And its equivalent transaction-level verilog is shown in the box in above image

The reason to $aa and not $a is just that the signal names in TL-verilog needs to be 2 characters, and not 1. There is an expression here for each bit of logic diagram shown below the code box (in above image). The “^2” represents a ‘square’ logic, a “+” represents ‘add’ logic and “sqrt” represents ‘square root’ logic. So in below expression, $aa_sq[31:0] = $aa ** $aa is square(a). Rest code should be self-explanatory

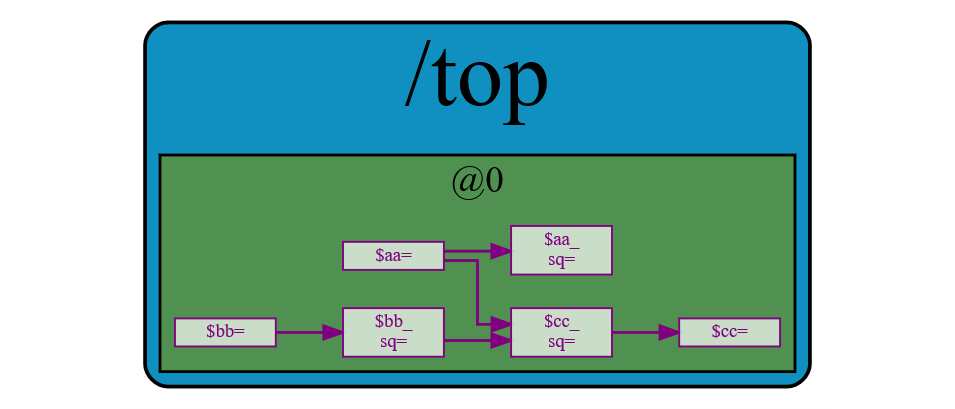

Next, we will copy paste the code in makerchip IDE and compile. We are doing this for the logic diagram, which is auto generated from Makerchip IDE. This is how the logic diagram looks like:

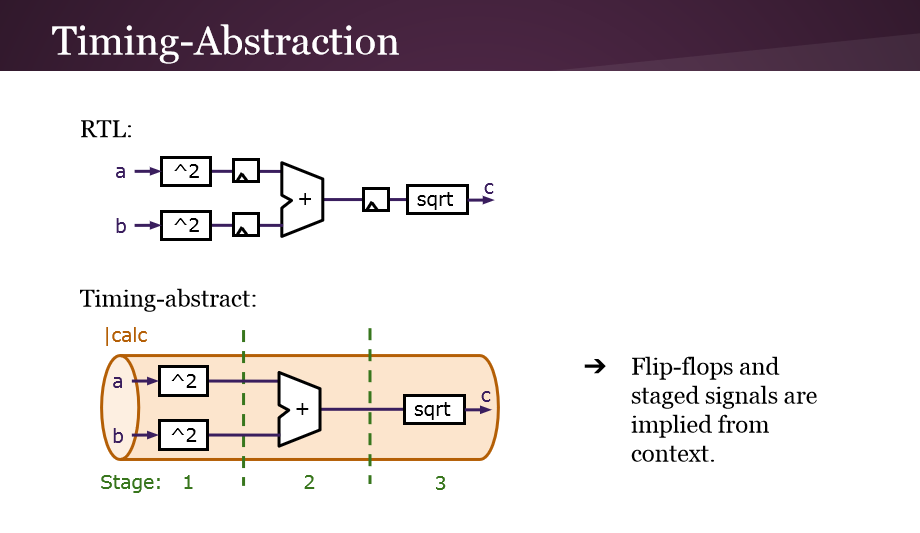

The above logic diagram matches the below in many ways. In TL-verilog, it uses an expression of logic, which is referred to as timing abstract. In RTL, we tend to have the mental picture of our design as shown under RTL tab in below image. And in TL-verilog, we tend to have a mental picture shown below the tab Timing-abstract in below image

In above image, under timing-abstract, we give ourselves a context of a pipeline and the pipeline is going to have stages 1, 2, 3. We are going to bucket our logic into those pipeline stages. Here, we are not bothering to draw flip-flops, explicitly. With this timing-abstract model, we don’t have to do that. Flip-flops are implied by the fact that I am drawing a wire from stage 1 to stage 2. The wire (perpendicular to vertical dashed line between stage 1 and 2) is a ‘$’ signal names, referred to as a pipe signal, which we have been using in TL-verilog and that pipe signal represent the signal assigned as well as all staged version of the signal

As depicted, lets give the above Pythagoras code, a context of pipeline using TL-verilog (And you will see how easy it is). Here’s the code:

\TLV

|calc

@1

$aa_sq[31:0] = $aa * $aa;

$bb_sq[31:0] = $bb * $bb;

@2

$cc_sq[31:0] = $aa+sq + $bb_sq;

@3

$cc[31:0] = sqrt($cc_sq);

\SV

endmodule

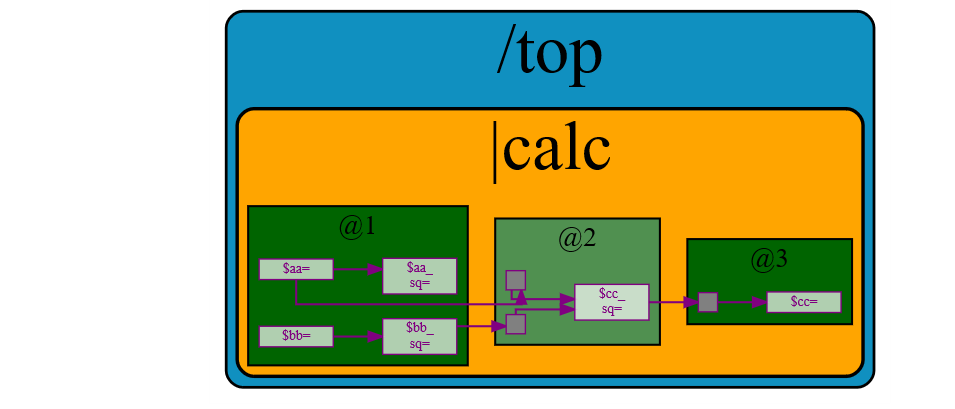

Once you compile the above code and investigate the logic diagram, you will see how beautifully makerchip has moved logics to different stages:

Now comes the magical part – the pipeline that we just created, below image shows the pipeline in TL-verilog (the one which we created above) and its corresponding verilog is on the right where you got explicit signal declarations for each of the individual wires, explicit flip-flops and the assignment statements.

Question – Who doesn’t want a 3.5X improvement in their code size? I guess everyone wants efficient and effective improvement. Now these are just few tips to have the easy implementation of pipe-line. You are free to implement your ideas in TL-verilog, compile, simulate and see the improvements on your own. For few more tips, you might want to check out below course on “VSD – Pipelining RISC-

V with TL-verilog”

https://www.udemy.com/vsd-pipelining-risc-v-with-transaction-level-verilog/

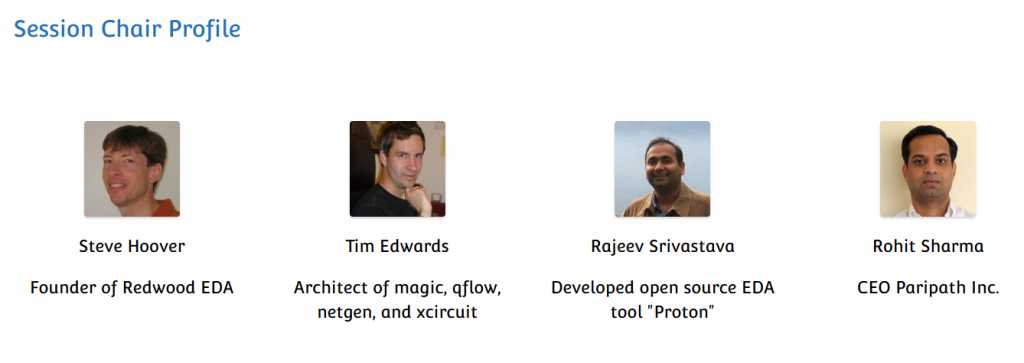

All your ideas will be reviewed by below panel of session chairs (who are all experts in their domains) and you might just get a chance to showcase your innovation to top crowd from VLSI industries:

The reason for this conference is to do out-of-the-box things in field of VLSI, to showcase your versatility and talent to a lot of TOP people, and get their attention, all online.

“This can be your new creative resume”

All the best for your submissions and happy learning