VSDOpen announces new technologies for effective VLSI skill development-2

If you have been following VSDOpen for the last 5-years, the theme has been maintained – What VSD did last year and what VSD will do next year

If you have been following VSDOpen for the last 5-years, the theme has been maintained – What VSD did last year and what VSD will do next year

It wasn’t that bigger deal for Intel because they thought, at the time, it will be 250,000 chips will be sold for 5 years, which isn’t that many. But they were wrong. It was a 100Million computers were sold. And suddenly 8086 from being an emergency back-up was an over-night success and had a very bright future, because it was binary compatible of PC software, and so had great opportunity

Isn’t that an inspiring story?

In last 50 years, there are 3 lessons that we can draw. First – software advances can inspire architecture innovations. Second – when we raise the hardware/software interface, it creates opportunities for architecture innovation. Third – in our field, the way we settle these debates, isn’t by just arguing in a bar, rather people spent/invest billions of dollars to investigate their ideas and marketplace settles these debates

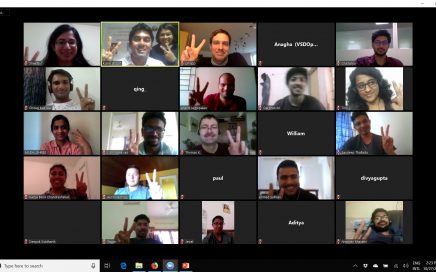

Hi “Pictures speak it all” Finally, we all did it – VSDOpen – first ever online VLSI conference. Very close to a real one – […]

“Design at $0” is an initiative driven by our team at VSD.Working in open environment is much easier process as all the resources are openly available, but here arise the loophole.

This paper introduces TL-V erilog and W ARP-V and then describes the formal verification of WARP-V using riscv-formal, a formal verification framework for RISC-V. Timing-abstraction and transaction-level design are showing significant benefits for hardware modeling, but this is the first demonstration of their benefits for verification modeling. As evidence of these benefits, the verification of all RISC-V configurations of WARP-V is accomplished in a single page of code.

Steve Hoover is the founder of Redwood EDA. Steve holds a BS in electrical engineering from Rensselaer Polytechnic Institute and an MS in computer science from the University of Illinois. He has designed numerous components for high-performance server CPUs and network architectures for DEC, Compaq, and Intel. Students will learn Transaction-Level Verilog modelingtechniques to generate Verilog models in half the time using the makerchip.comfree online IDE. A new open-source RISC-V CPU development effort will be introduced that showcases flexible IP design practices.

Design Verification is critical to proving functional correct- ness and establishing confidence in a design. Several stud- ies from industry and academia, particularly over the course of the last two decades, have explored various verifica- tion methodologies that fall somewhere between dynamic or purely static formal approaches.

System-on-Chips (SoCs) today have become extremely complex structures housing heavily optimized cores, count- less peripherals, and large interconnect fabrics. Even re- stricting ourselves to just verifying the microprocessor, the state space to be verified is enormous and cannot be exhaus- tively explored in any finite amount of time. Manually writ- ten tests, while effective at capturing some complexities of design intent, suffer from the fact that they are expensive in cost and time required to develop them. Random stimulus methods perform better because they eventually cover many cases. Most new ideas in dynamic verification over the last two decades have largely been towards semi formal verifi- cation methodologies such as coverage driven verification and constrained test generation. In this paper, we explore an approach to dynamic functional verification that we use at the RISE lab, IIT Madras for the verification of the RISC-V based Shakti cores.

A simple chip frequency divider but most prominently used in counter modules of a microproceesor or as standalone IC can be completely designed from Verilog code to layout . A complete chip with IO pins and labels on it can be designed with help of efabless cloud based eda tool just like a commercial IC. There are two toolbox in efabless one is CloudV for Verilog or c code & other is Open Galaxy for backend design for designing commercial like IC with zero cost involved & same can be given to Semiconductor foundries for mass production. From Preparation , synthesis to DRC cleanup using Q flow manager a Core part of IC can be obtained with log files of each stage used in this process. A innovative feature of interactive DRC under Magic tool enables the designer to rectify DRC violations on the spot. Moreover, ESD protection is also available under Opengalaxy tool for use of chip in electrosensitive applications.

Mohamed Kassem is the CTO and Co-Founder of efabless.com, the first semiconductor company applying open community innovation to all aspects of product development. Prior to launching efablesshe […]