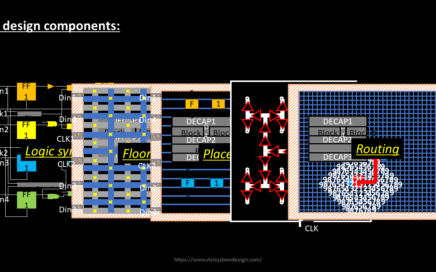

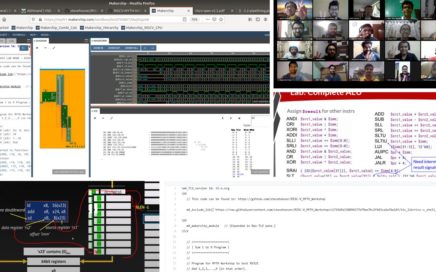

Foundry IP’s vs Macros – 10years to solve this query

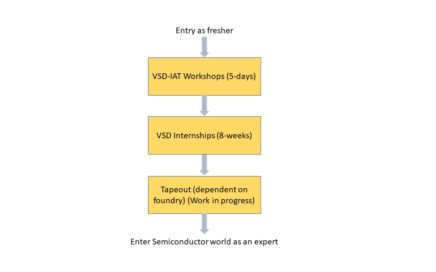

A great one – not only for VSD, but also for entire VSD community. The journey has just begun, in nutshell, below image shows a well-designed VLSI Skilling model (VSD Workshops + VSD-IP design Internship + Tapeout[working on it]), which is not just participants driven but also silicon proven. To summarize, given a problem statement, VSD Interns and participants, who have gone through this rigorous training and designing model will have much better ways to figure out solutions by themselves.