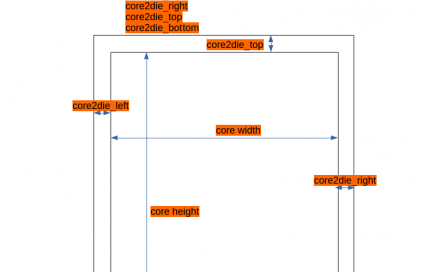

Let’s re-think open-source EDA – core and die

Hey There – Think about it!!! Today’s version of open-source EDA tools, work very well for hierarchical designs sub-25k instance count. For hierarchical designs ~500k […]

Hey There – Think about it!!! Today’s version of open-source EDA tools, work very well for hierarchical designs sub-25k instance count. For hierarchical designs ~500k […]

Online university Course name – Foundation of Computer Systems Design

This course is being taught by Prof. V. Kamakoti, who needs no introduction, who lead India’s first RISC-V microprocessor SHAKTI teamand made all of us proud.

With learning being online, SHAKTI core and ‘vsdflow’ being opensource, this is first-time in the history of VLSI design & EDA (thanks to RISC-V ecosystem and Shakti Team at IITM lead by Prof. Kamakoti), a chip will ever be taped-out using all open source flow, which will cater to almost 80% Indian Semiconductor Market.

It wasn’t that bigger deal for Intel because they thought, at the time, it will be 250,000 chips will be sold for 5 years, which isn’t that many. But they were wrong. It was a 100Million computers were sold. And suddenly 8086 from being an emergency back-up was an over-night success and had a very bright future, because it was binary compatible of PC software, and so had great opportunity

Isn’t that an inspiring story?

Hi Vlsi

Your feedback has been continuously pushing us to the edge. And I really want to Thank You for all the support you have been giving over the past. Its due to this push, we are now releasing (especially for VLSI freshers), a package, which you just need to download/run. That would install all opensource EDA tools on your UNIX machine plus run a complete RTL-2-GDS on RISC-V core ‘picorv32’.

All you need to do is go to below github link, and follow simple 5 steps given in the README of below link:

In last 50 years, there are 3 lessons that we can draw. First – software advances can inspire architecture innovations. Second – when we raise the hardware/software interface, it creates opportunities for architecture innovation. Third – in our field, the way we settle these debates, isn’t by just arguing in a bar, rather people spent/invest billions of dollars to investigate their ideas and marketplace settles these debates

Hi “Pictures speak it all” Finally, we all did it – VSDOpen – first ever online VLSI conference. Very close to a real one – […]

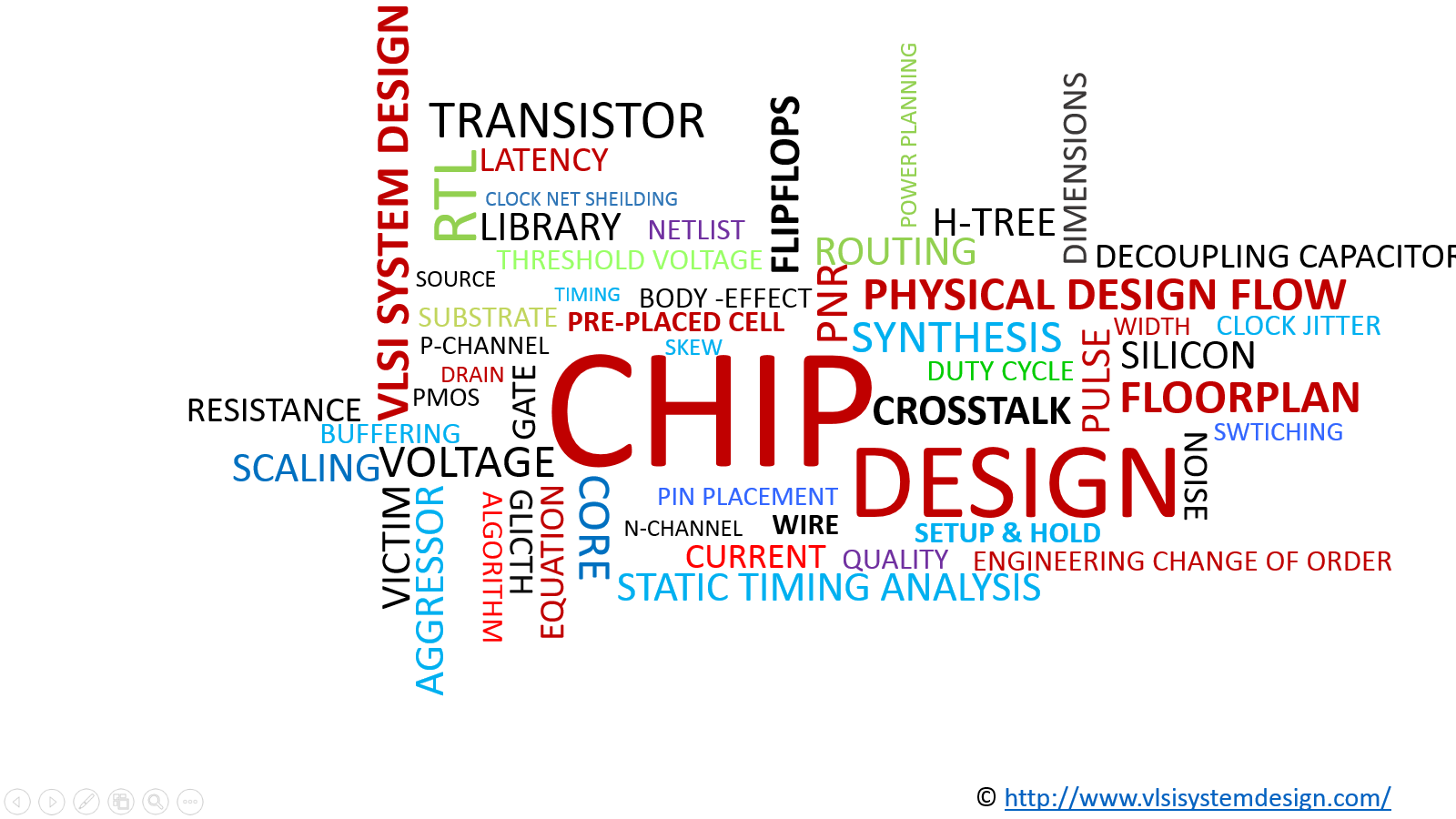

“Design at $0” is an initiative driven by our team at VSD.Working in open environment is much easier process as all the resources are openly available, but here arise the loophole.

Transaction-Level Verilog (TL-Verilog) is an emerging extension to SystemVerilog that supports transaction-level design methodology. In transaction-level design, a transaction is an entity that moves through a microarchitecture. It is operated upon and steered through the machinery by flow components such as pipelines, arbiters, and queues. A transaction might be a machine instruction, a flit of a packet, or a memory read/write. The flow of a transaction can be established independently from the logic that operates on the transaction. We present a preliminary library of TL-Verilog flow components that can be quickly stitched together to establish a complete microarchitecture. We show how transaction logic, like packet decoding, can be added within this flow.

This paper introduces TL-V erilog and W ARP-V and then describes the formal verification of WARP-V using riscv-formal, a formal verification framework for RISC-V. Timing-abstraction and transaction-level design are showing significant benefits for hardware modeling, but this is the first demonstration of their benefits for verification modeling. As evidence of these benefits, the verification of all RISC-V configurations of WARP-V is accomplished in a single page of code.