The Raven chip: First-time silicon success with Qflow and Efabless

- Raven is a open-source top-level SoC design based on an open-source RISC-V core

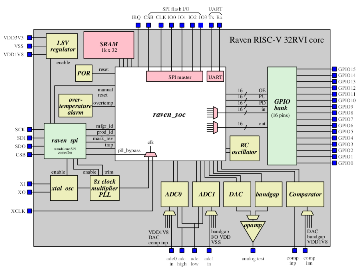

- Complete SoC design including digital and analog IP

- Build using a open-source design flow

- Successfully implemented in silicon using X-FAB’s 180nm XH018 process

- The project is available through Github including test benches and development board

- Users can also clone the project on the Efabless platform to create derivative designs

- The raven chip contains two ADCs, a DAC, comparator, bandgap, RC oscillator, and over-temperature alarm, as well as 16 bits of general-purpose digital inputs/outputs.

- It is powered off of a single 3.3V supply and driven by a 5 to 12 MHz crystal. The core CPU clock speed is 8 times the crystal frequency.