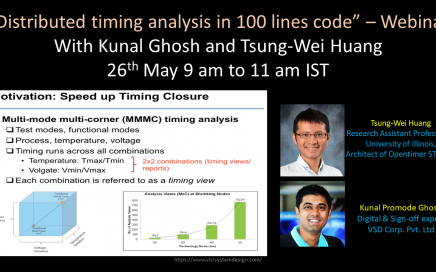

A prestigious day for us…It can be for you..

A proud moment for our company VLSI System Design Corporation Pvt. Ltd., for my colleague Anagha Ghosh and for myself (See image below)

Our company’s first paper on IEEE explore for technology mediated learning – World’s prestigious institute for engineering and technology innovation. Here’s the link for the paper

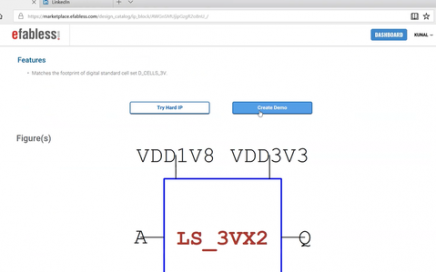

https://www.vlsisystemdesign.com/vsdlibrary/