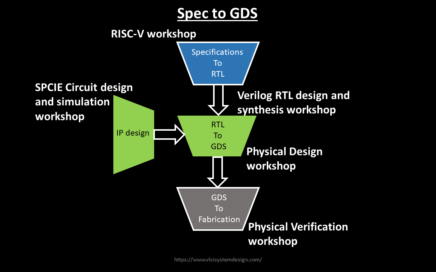

Skywater130 Spec to GDS workshop details

You might have seen the above image in one form or another, in different our blogs or VSD websites. Every trapezoid in above image is […]

You might have seen the above image in one form or another, in different our blogs or VSD websites. Every trapezoid in above image is […]

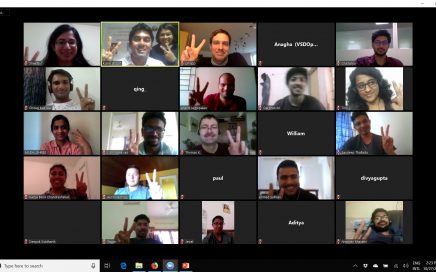

Hi “Pictures speak it all” Finally, we all did it – VSDOpen – first ever online VLSI conference. Very close to a real one – […]

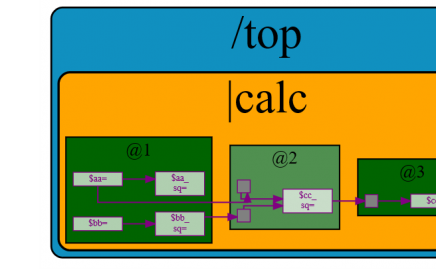

This paper introduces TL-V erilog and W ARP-V and then describes the formal verification of WARP-V using riscv-formal, a formal verification framework for RISC-V. Timing-abstraction and transaction-level design are showing significant benefits for hardware modeling, but this is the first demonstration of their benefits for verification modeling. As evidence of these benefits, the verification of all RISC-V configurations of WARP-V is accomplished in a single page of code.

Steve Hoover is the founder of Redwood EDA. Steve holds a BS in electrical engineering from Rensselaer Polytechnic Institute and an MS in computer science from the University of Illinois. He has designed numerous components for high-performance server CPUs and network architectures for DEC, Compaq, and Intel. Students will learn Transaction-Level Verilog modelingtechniques to generate Verilog models in half the time using the makerchip.comfree online IDE. A new open-source RISC-V CPU development effort will be introduced that showcases flexible IP design practices.

Question – Who doesn’t want a 3.5X improvement in their code size? I guess everyone wants efficient and effective improvement. Now these are just few tips to have the easy implementation of pipe-line. You are free to implement your ideas in TL-verilog, compile, simulate and see the improvements on your own. For few more tips, you might want to check out below course on “VSD – Pipelining RISC-

V with TL-verilog”

Hello And, finally, we have a video on what we posted on this topic. Below is the snippet of the same. Full video can be […]

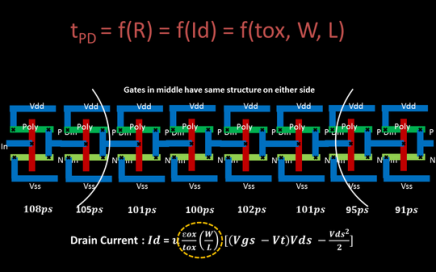

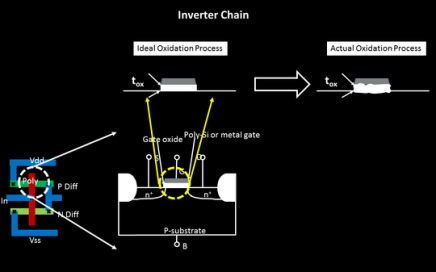

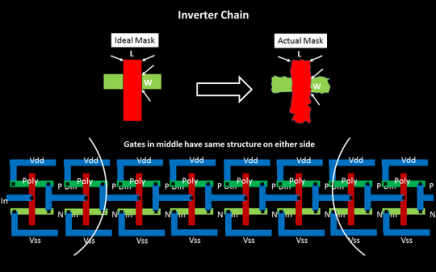

Hello, The below image models “low-to-high waveform condition” at input of CMOS inverter, in terms of resistances and capacitance. So, overall, its the RC time […]

Hello Today, I was a guest speaker at one of the biggest Technical Conference held in Bangalore, and luckily I met few people who had […]

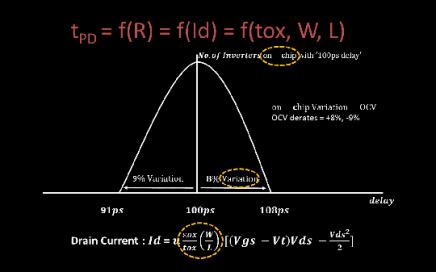

Hello Ever thought what’s an interviewer’s favorite questions to rip you off – all of my previous post :). And On-Chip Variation (OCV) is one […]