Hello,

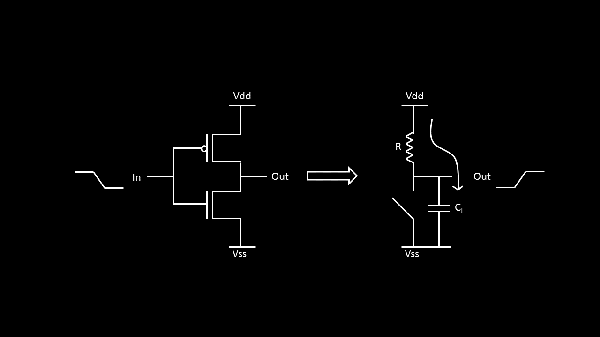

The below image models “low-to-high waveform condition” at input of CMOS inverter, in terms of resistances and capacitance.

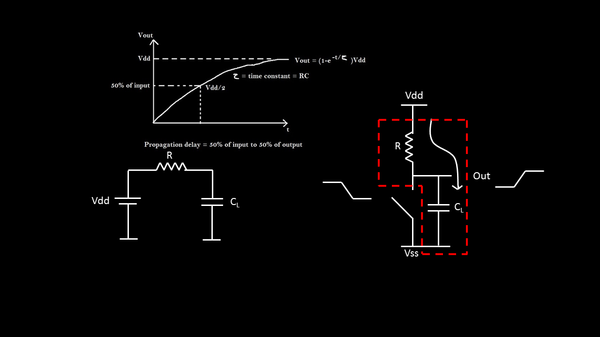

So, overall, its the RC time constant that actually decides the delay of a cell

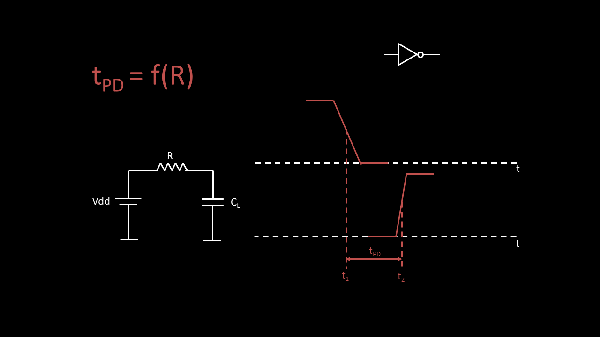

With above, we can safely say, the propagation delay tPD is a function of ‘R’

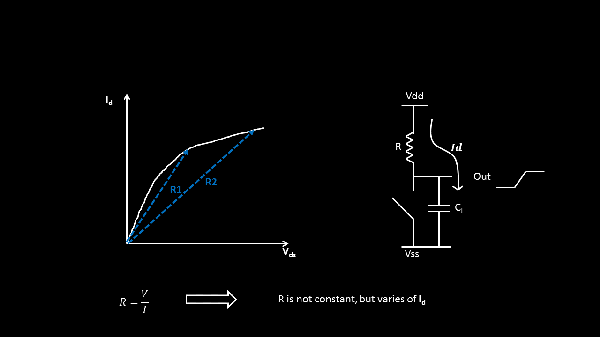

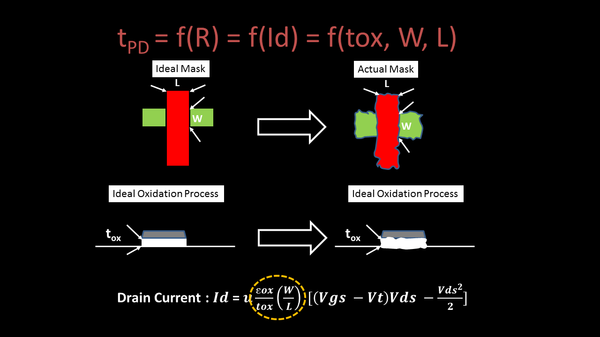

Now, from previous posts, we seen variation in drain current ‘Id’ due to variation in ‘W/L’ and ‘oxide thickness’ variations, and above we see, how propagation delay is function of ‘R’.

The question is now, what next?. If I am, somehow, able to prove, that drain current ‘Id’ strongly depends on ‘R’, then I can directly relate (W/L) and oxide thickness variation to ‘R’, and below images will exactly do that

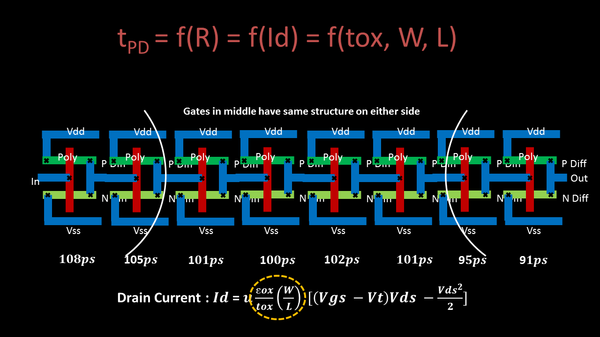

Hence, every inverter in the below chain, will have delay which is different than the immediate next one, something like below

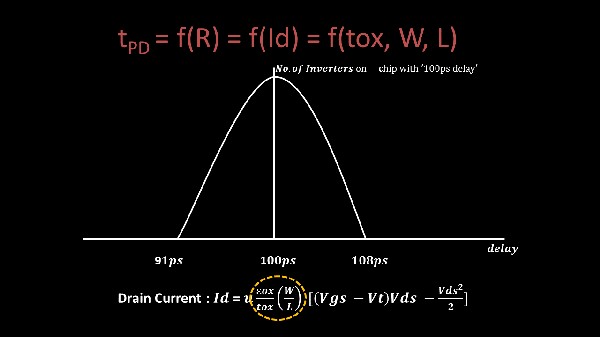

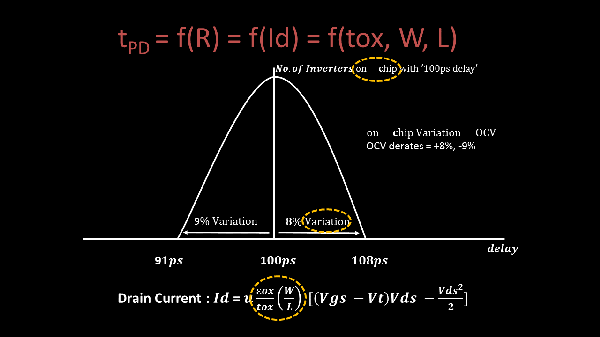

If we plot a Gaussian Curve with delays on x-axis and no. of inverters on y-axis, it will give us a clue, about the peak variation in inverter delays, the minimum and maximum variation in inverter delays like below

Now, we know the percentage variation in delays of inverter compared to ‘100ps’, because that’s where the inverter delay (with used ‘W/L’ ratio) is expected to be, and most number of inverters on chip with that ‘W/L’ ratio have a delay of 100ps

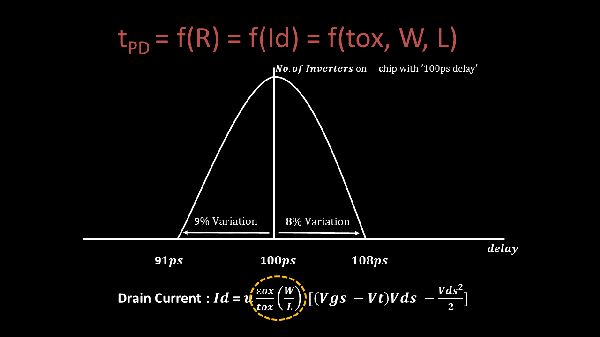

OCV variation is +8% and -9% and one of them will be used for launch and other for capture in setup/hold timing calculations.

For eg. for setup calculation, the launch clock will have OCV of +8% and capture clock path will have OCV of -9%. That means, if the original clock cell delay is ‘x’ in launch clock, with OCV into account, the same clock cell delay will be (‘x’ + 0.08x). This calculation in setup takes into account the On-Chip Variation, and that’s where the name comes from, as shown below

the images in above post and the previous one’s makes this concept so simple. Isn’t it? But, keeping things simple is the most difficult job 🙂 I took around 3 weeks, just to make these images. Please … kudos to ME 🙂 :).

For me, solving any concept, is just like a war. Ulysses S. Grant rightly mentions“The art of war is simple enough. Find out where your enemy is. Get at him as soon as you can. Strike him as hard as you can, and keep moving on“

My next post, will be on CPPR (Clock Path Pessimism Removal), which will apply the concept of OCV in STA.

Thanks

Kunal