A combinational circuit is an electronic circuit in which the output of the circuit is a function of the current inputs only, and not of the past inputs or outputs. This means that the output of a combinational circuit depends only on the current state of its inputs, and not on any previous input or output states.

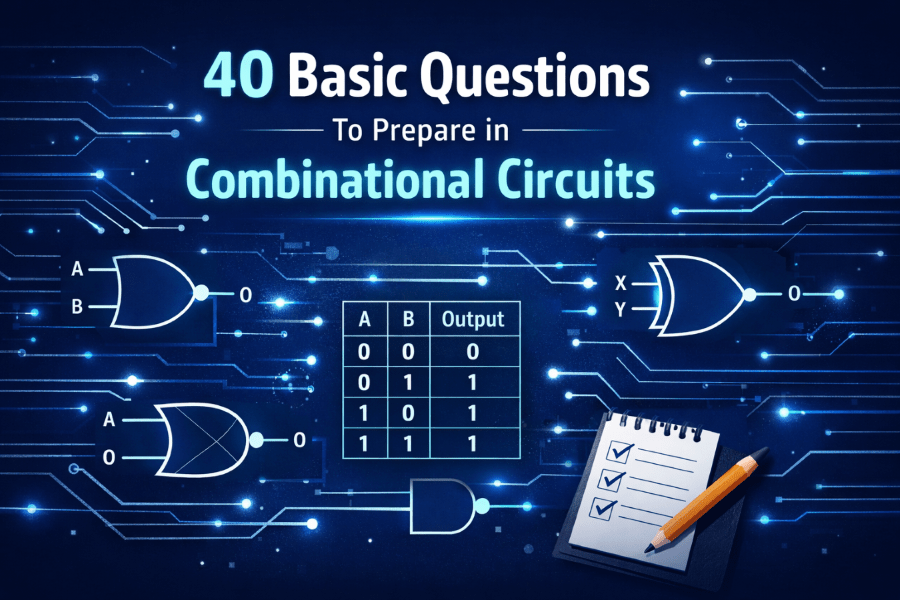

Combinational circuits are commonly used to perform logical operations, such as AND, OR, and NOT, on binary inputs. They are also used to implement digital circuits that perform arithmetic operations, such as addition and subtraction, and to implement digital circuits that perform data manipulation, such as data encoding and decoding.

Combinational circuits can be designed using a variety of electronic components, such as logic gates, multiplexers, and decoders. They can be implemented using discrete electronic components, such as transistors and resistors, or using integrated circuits, such as logic gates and multiplexers.

Combinational circuits are an important part of digital electronics and are widely used in a variety of applications, including computer systems, communication systems, and control systems.

Combinational circuits and sequential circuits are two types of digital circuits that are used to perform different types of operations.

Combinational circuits are digital circuits in which the output of the circuit is a function of the current inputs only, and not of the past inputs or outputs. This means that the output of a combinational circuit depends only on the current state of its inputs, and not on any previous input or output states.

Sequential circuits, on the other hand, are digital circuits in which the output of the circuit is a function of both the current inputs and the previous inputs and outputs. This means that the output of a sequential circuit depends on both the current state of its inputs and its previous states.

One of the main differences between combinational circuits and sequential circuits is that combinational circuits do not have memory, while sequential circuits have memory. This means that combinational circuits cannot store information about past inputs or outputs, while sequential circuits can store this information in the form of flip-flops or other types of memory elements.

Another difference between combinational circuits and sequential circuits is that combinational circuits are typically faster than sequential circuits, since they do not have the overhead of storing and retrieving data from memory. However, sequential circuits are more versatile than combinational circuits, since they can perform a wider range of operations, including data storage, data manipulation, and decision making.

Combinational circuits are commonly used to perform logical operations, such as AND, OR, and NOT, on binary inputs, and to implement digital circuits that perform arithmetic operations, such as addition and subtraction. Sequential circuits, on the other hand, are commonly used to implement digital circuits that perform data manipulation, such as data encoding and decoding, and to implement digital circuits that perform decision making, such as controllers and finite state machines.