Let’s see how

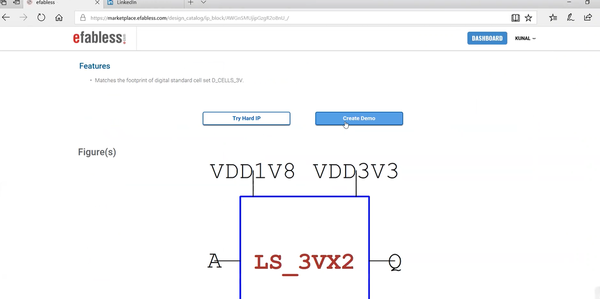

Click on “Create Demo” as shown in below image:

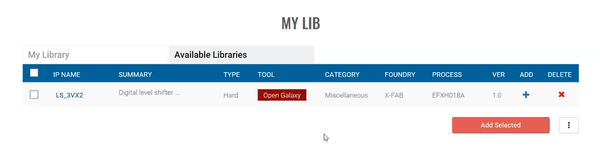

Then it will say, it has been added to “My Lib”. Click the blue cross in below image under “ADD” column:

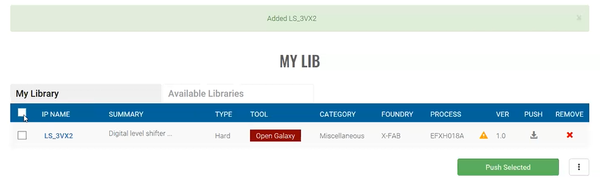

This means it’s now part of your library. And below is what you would see. But there is a second stage you need to do

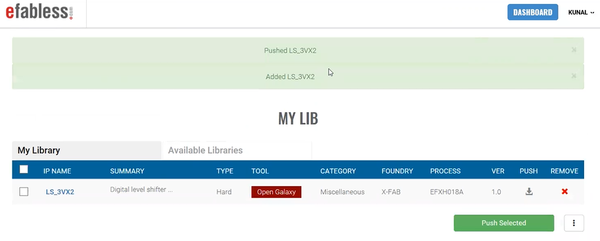

You need to click on the “Push” button, wait a few seconds, and will tell “Pushed” as shown below:

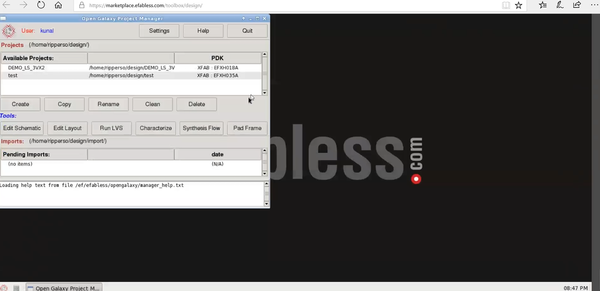

Now its synchronized to your open-galaxy account. Click on “Open Galaxy”, the red button shown in above image. And below is what the desktop looks like:

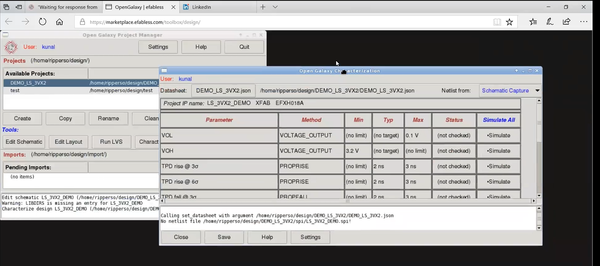

As you see above, you can run schematic, layout, LVS and characterize. Characterize is what we are interested in. Click on “Characterize” and below is what you would see:

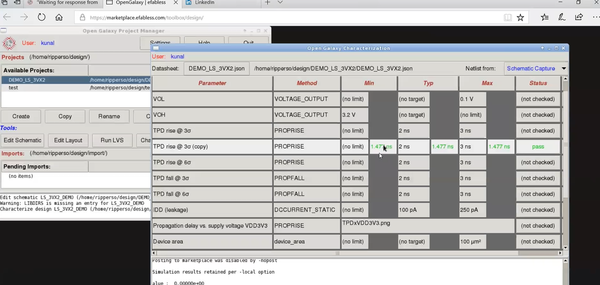

And now, when you click on “Simulate All”, it will give you all parameters which are being shown in a standard data-sheet. For eg., click on “Simulate” for propagation delay TPD rise, and below is what you will see.

It will show up delays for min, max, typ: Aren’t these the corners that you see in an STA analysis? Yes, they are.

Isn’t that a simpler way to run and view characteristics of any IP or standard cell? Well, that’s was just a demo of the powerful efabless platform. Do you want to know more about this powerful yet simple platform? Do you want to build complete SoC using this platform? We did an entire webinar on this, and here’s the copy of it. Get it at $9.99 for next 12 hours and explore/innovate with efabless platform

“The future belongs to the curious. The ones who are not afraid to try it, explore it, poke at it, question it and turn it inside out”