Don’t get scared or excited by above image. We are not even close…

We just launched our new course on Machine Intelligence in EDA/CAD, below is the link/image for your reference.

https://www.udemy.com/vsd-machine-intelligence-in-eda-cad/?couponCode=LAUNCHED_NOW

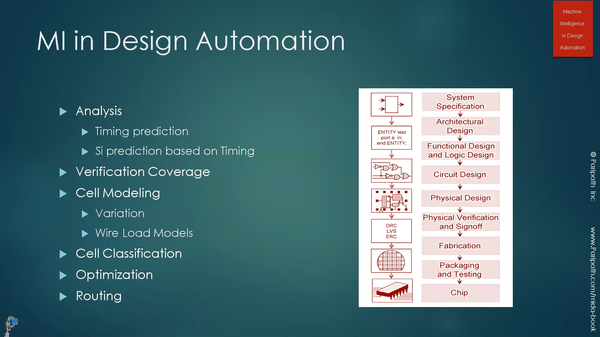

Just to get a start on this, first, let’s identify what has happened till date in field of EDA/CAD using Machine intelligence. The image below shows the flow diagram for designing a chip. This is what has happened (or happening) in EDA using machine intelligence

Analysis

Timing prediction – Without doing timing analysis, based on what you have seen in the chips that were taped out before, of similar size and on the same node, you can predict the timing of chip way early in the flow.

SI prediction – There was a paper written by Andrew Kahng from UCSD in 2017, that despite doing timing analysis, you can do SI for FREE. You don’t have to do noise analysis. It will predict noise based on timing results. Here’s the link to the presentation:

http://vlsicad.ucsd.edu/Presentations/talk/Kahng-ANSYS-DACBreakfast_talk_DISTRIBUTED2.pdf

Verification coverage

The idea here is essentially to predict what kind of coverage you are going to get with the test bench you are writing. This kind of application works in the loop where its collecting the data as you are feeding your testbenches to the verification engine and on the side, it provides the model which you can use and ask, if I run it for next 8 hours, what kind of additional coverage I am going to get. It tells you within minute (may be within seconds), that this is going to get you 5% after 90%. It’s a quick way to get the feedback

Cell modeling

Variation – Cell modeling has been around for almost a decade now. Variation was used by Solido. In their product, they were using a core algorithm called PCA (principal component analysis) which looks at the sensitivities of the SPICE model and finds out which variation parameters are affecting the models, timing and power modes and the rest. It studies those and uses PCA. PCA is an algorithm whereby it reduces the dimensionality of the problem and creates new parameters for the simulations which are fed to your SPICE and the simulation is performed in a lot less time like 10x faster

Wire load models – This is a simple enough application to cover in one webinar (which we launched yesterday on Udemy). There are more complex things which you can predict. They could be just for placement, where can predict the whole RC tree using regression, complex kernel-based regression scheme

Cell Classification

This is essentially a pattern identification engine which uses classification algorithm. This is covered in detail in below webinar we uploaded yesterday. (Look for below link in my course catalogue)

Optimization

This is essentially a functional mapping from machine learning point of view, whereby it maps the inputs and outputs to speed up the optimization engine.

Routing

There was a paper from Stanford, last year 2017 October, whereby neural network was actually trained to find the detailed route between cells. Here’s the paper:

https://arxiv.org/pdf/1706.08948.pdf

These are some of the things which we know. There might be more exciting things as we continue our research in design automation

Want to get real insights on Machine Learning in VLSI? Here’s the link to the complete webinar conducted by Rohit Sharma, CEO of Paripath. Inc

https://www.udemy.com/vsd-machine-intelligence-in-eda-cad/?couponCode=LAUNCHED_NOW

All the best and happy learning…