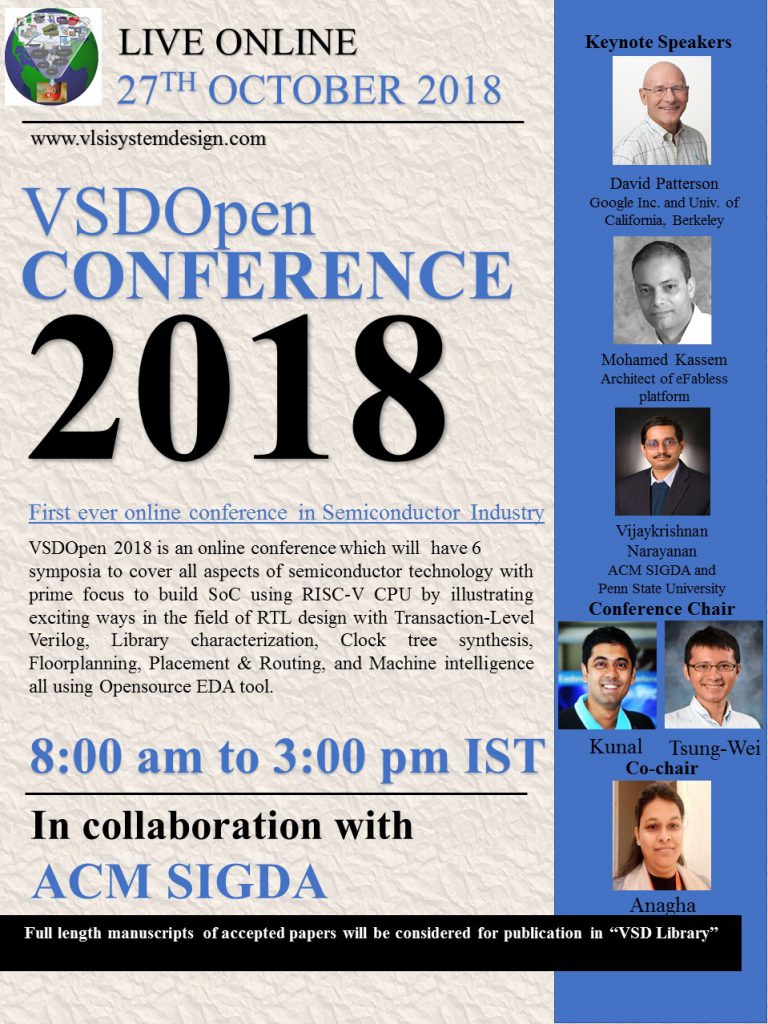

Plan now to participate in VSDOpen Conference 2018, first ever online conference for showcasing the Semiconductor technology and design developed in Open source environment. VSDOpen will be held online on 27th October 2018 in collaboration with ACM SIGDA.

VSDOpen 2018 is an online conference which will have 6 symposia to cover all aspects of semiconductor technology with prime focus to build SoC using RISC-V CPU by illustrating exciting ways in the field of RTL design with Transaction-Level Verilog, Library characterization, Clock tree synthesis, Floorplanning, Placement & Routing, and Machine intelligence all using Opensource EDA tool.

**Full length manuscripts of accepted papers will be considered for publication in “VSD Library”

- VSDOpen 2018 is one of its kind first online conference in VLSI and semiconductor industry.

- VSDOpen 2018 focus on open forum for innovation in the field of chip design and IP development inclusive of emerging technologies at lower nodes.

- The symposium will be an international forum where many of the world’s leading open source experts and professionals from both industry and academia join to present and discuss key development in design using open source EDA tools.

- VSDOpen 2018 addresses key trends and challenges in the open source EDA tools used to do semiconductor design and vlsi industries through an exciting program that includes Keynote, Technical Paper Sessions,online networking.

Date & Venue: LIVE ONLINE on 27th October 2018 at 8:00 am to 3:00 pm IST.

Distinguished Conference Keynote Speakers

David Patterson

Google Inc. and

Univ. of California, Berkeley

Mohamed Kassem

Architect of eFabless platform

Vijay Narayanan

ACM SIGDA and Penn State University

Conference Keynote Speakers Profile

David A. Patterson

Biography: After 40 years at UC Berkeley, David Patterson became an Emeritus Professor and started working in Google Brain. He is also Vice-Chair of the RISC-V Board of Directors. He has been Chair of Berkeley’s CS Division, Chair of the Computing Research Association, and President of the Association for Computing Machinery. His most successful research projects have been Reduced Instruction Set Computers (RISC), Redundant Arrays of Inexpensive Disks (RAID), and Network of Workstations. This research led to many papers, seven books, and about 40 honors, including the ACM Turing Award, IEEE von Neumann Medal, member of the National Academy of Engineering, the National Academy of Sciences, the Silicon Valley Engineering Hall of Fame, and Fellow of the Computer History Museum and both AAAS societies. At Berkeley he is interested in computer architecture to improve security and at Google he helps with future Tensor Processing Units (TPUs).

Mohammed Kassem

Biography: Mohamed Kassem is the cofounder and CTO of eFabless corporation. Prior to launching eFabless in 2014, Mohamed held several technical and global leadership positions within TI's Wireless Business Unit. He joined TI in 2000 at the beginning of the digital telephony revolution fueled by the unprecedented integration of major phone functions on a single SoC.He led the first development of 45nm, 28nm analog & mixed-signal IP functions for wireless applications processors. Mohamed holds a Masters degree in Electrical Engineering from the University of Waterloo, Ontario, Canada.

Vijay Narayanan

Biography: Vijay Narayanan is a Distinguished Professor of Computer Science & Engineering and Electrical Engineering at the Pennsylvania State University. Vijay received his Bachelors in Computer Science & Engineering from University of Madras, India in 1993 and his Ph.D. in Computer Science & Engineering from the University of South Florida, USA, in 1998. He is a co-director of the Microsystems Design Lab.

List of Symposium

VSDOpen 2018, the six hours program, responds to many trends and challenges in semiconductor design using open source hardware tools and developing the IP to reach the silicon level, with papers and presentation in the research paper sessions covering the core set of design topics: Front-end open-source EDA tool flows for IC design and verification, Clock tree synthesis and optimization of digital IC’s for best Performance, Floorplanning of digital IC’s for best area, Place and Route of digital IC’s for best PPA, Standard cell layout/characterization for compact area/high performance/minimal routing resources, Machine Learning in EDA.

Sr.no |

Subject |

Session Chair |

| 1. | Front-end open-source EDA tool flows for IC design and verification

•Focus: Application oriented SoC using RISC-V as CPU, cloud FPGA •Tools: TL-Verilog (HDL), Makerchip (IDE), Verilator (compiler/simulator) |

Steve Hoover |

| 2 | Clock tree synthesis and optimization of digital IC’s for best Performance

•Focus: Clock tree strategy for complex RISC-V CPU to achieve best performance in terms of skew and pulse width •Tools: qyosys (Synthesis), vesta or Opentimer (STA), ngSpice or eSim (SPICE simulations) |

Tim Edwards |

| 3 | Floorplanning of digital IC’s for best area

•Focus: Floorplanning for RISC-V CPU like picoRV32/E31_coreplex_IP to achieve best area •Tools: Proton (Floorplanning, pin-placement, macro/memory/ip pre-placement, aspect ratio) |

Rajeev Srivastava |

| 4 | Place and Route of digital IC’s for best PPA

•Focus: PNR strategy for complex blocks/full chip to achieve best PPA and runtime •Tools: Proton or qflow (PNR), vesta or Opentimer (STA) |

Rajeev Srivastava/Tim Edwards |

| 5 | Machine Learning

•Focus: Applications of EDA and CAD •Tools: Google Cloud Infrastructure including Collaboratory research |

Rohit Sharma |

| 6 | Standard cell layout/characterization for compact area/high performance/minimal routing resources

•Focus: Layout/Characterization of standard cells/IP’s using Magic/Guna •Tools: Magic (layout), Guna (lib char), ngSpice (SPICE simulations) |

Tim Edwards & Rohit Sharma |

Paper submission Timeline

|

VSDOpen 2018 will be LIVE on 27th October 2018 |

||

|

Timeline Date |

Details |

|

| Call for Paper |

1st June 2018 |

Author must use the ABSTRACT TEMPLATE. Word limit up to 1000 words. The abstract must clearly describe the nature, scope, content, organization, key points and significance of the proposed papers. |

| Abstract Submission Due |

15th August 2018 |

Abstract submitted after the submission deadline will be considered on a case-by-case basis. |

| Abstract Acceptance Notification sent |

15th September 2018 |

Primary authors/contacts will receive an instructional email. Upon notification, authors will be requested to confirm their participation in the conference. |

| Manuscript Due |

15th October 2018 |

All authors, regardless of session, are required to submit a preliminary/draft manuscript using the approved MANUSCRIPT TEMPLATE with the filename as 'VSDOpen'18_Symposium ID_Author' (ID: Serial Number). Once completed, preliminary must be send to the VSD at vsd@vlsisystemdesign.com in Word version. |

| Camera ready and author's registration last day |

22nd October 2018 |

Speakers are responsible for providing a PPT in advance to be uploaded for presentation at the conference. We encourage speakers to use the VSDOpen'18 Template.Send PPT to vsd@vlsisystemdesign.com |

| Speaker/ Presenter Registration Online |

22nd October 2018 |

$10 for all speakers/presenters/LIVE audience. |

| Conference Date |

27th October 2018 |

All VSDOpen 2018 speakers/presenters who attend the conference must register.

|

Conference Chair

Co-Chair

Kunal Ghosh

Digital and Sign-off expert

& Co-founder VSD Inc.

Tsung-Wei Huang

PhD University of Illinois

at Urbana-Champaign

Anagha Ghosh

Founder VSD Inc.

Session Chair Profile

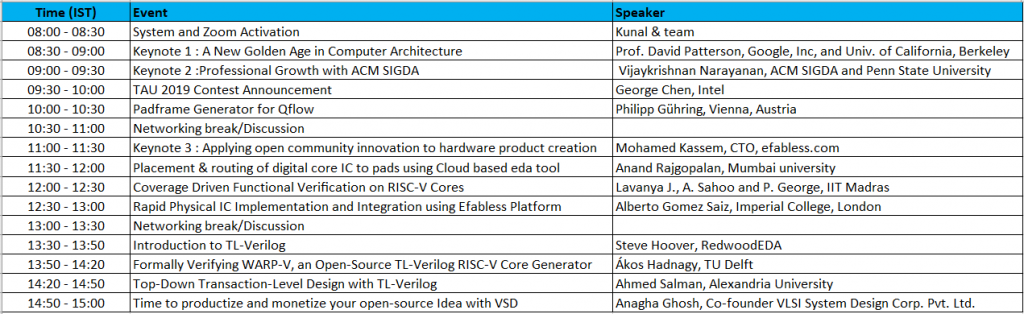

Event Schedule :

Buy the recorded version of VSDOpen Conference 2018:

Presentation of the video courses powered by Udemy for WordPress.