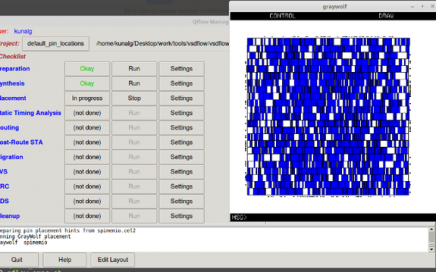

‘vsdflow’ on CentOS is ready

to build the shell script for ‘vsdflow’ on CentOS, and finally I have the first cut ready. You just need to follow steps given in below link for CentOS, and all opensource EDA tools (PNR, STA, Layout, LVS) will be installed on your system. There are 2 testcases (picorv32 and spi_slave) inside the below link to test whether all tools have been installed or not. After running the shell script in below link, you need run the testcase