If that’s not all, I am going to surprise you even more…A working chip is all using opensource EDA tools (no more license fee). Of course, its taped-out in 180nm technology. But who knows, this might be just the beginning. Upcoming blogs will talk more about the commercial angle of this. Let’s see how it is going to benefit student/professionals/innovators community.

Say, you have an idea of a processor. Now, you want to measure the performance and area of your processor, so that you can plan your entire chip. What would you do? What are the EDA tools available right now to estimate the area and performance of chip which visually see it? (You can’t view and design your whole chip in chipestimate website) Just like web designing, how do you achieve the famous WYSIWYG (what-you-see-is-what-you-get) concept?

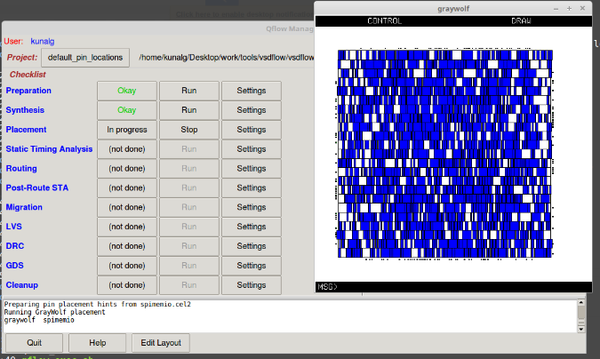

The below GUI (currently running “Placement” stage) has been very specifically designed for simplicity, so that for designers, its just a PUSH button and need not worry about specifics. I can guarantee this, because I have used for one of my blocks (spimemio), and it works like magic.

There’s also an option, where you need to do a pre-route timing analysis, just to check the quality of your placement database, and there’s a button “Static Timing Analysis” just below the “Placement” button, which will give you an overview of performance of your placed design

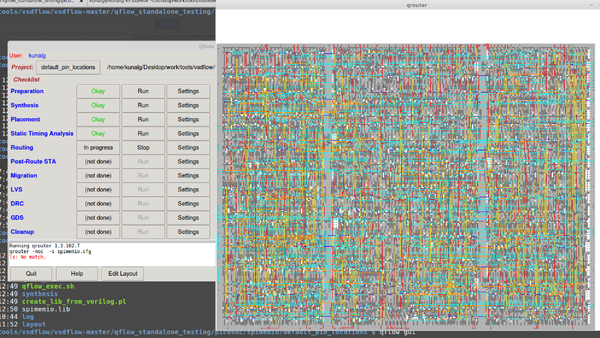

Next, you go to routing step (with default settings) and it seamlessly launches router, while you sit back and wait for your routed database to come out. Here’s what the routing step looks like:

Then, finally, you need to do post-processing steps, like post-route STA, DRC, LVS and create GDS for tape-out. This example makes it obvious, that running a tool is easy, but planning on how to run a tool, tune it and make it work for your own designs is a difficult job.

That’s where you would need the below webinar, in which we start from a point, where we stopped in previous webinar by eFabless (we had planned SOC top level). We will take and continue with the same design, tune our tool to make sure, it places and routes the design the way we want it to and get the best results in terms of performance/area

Here’s the link (scroll down till end of below page) to enroll in our 4-hour webinar happening on 2nd June from 9am to 1pm IST:

https://www.vlsisystemdesign.com/upcoming-event/

(Limited seats, first-come-first-serve basis, to maintain uniform load on server for labs)

Note – Once you enroll, email your confirmation ticket to [email protected] and I will enable 1 of my 24 courses for free for you

All the best and happy learning….