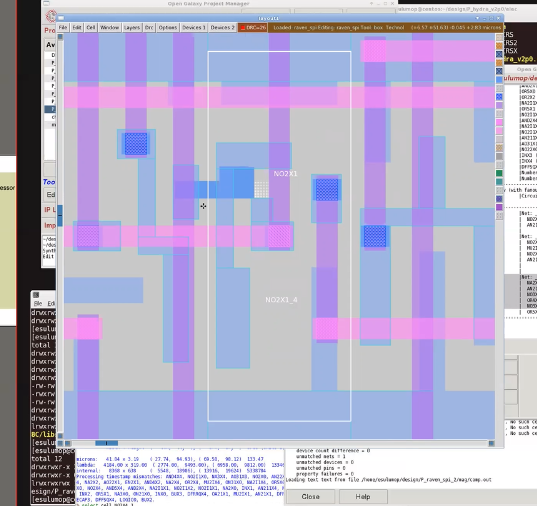

DRC is something which (most likely) is supposed to fail in first instance. Let’s see what you do to fix them. In below eg. drc count is 25. Qrouter (an open-source router, which will be discussed in detail in webinar) is really good with some standard cell sets like the one which comes distributed with qflow, like OSU018, they are really nice one’s to work with. All the ports have nice squares, they don’t have these inside ‘L’ corners as shown below.

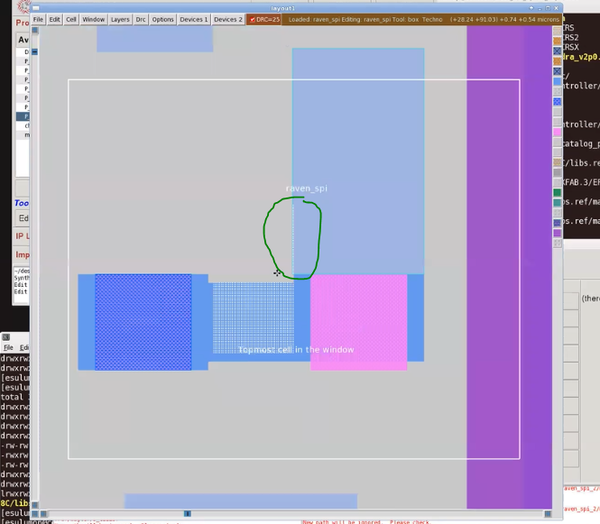

If I want to go and fix them, we need to go “DRC find next error” under DRC tab in below image. So, this is the sort of thing that shows up a lot, here’s the notch error. It tried to put down a contact on left and right (shown by square boxes in below image), tried to route between them and ended up creating a notch.

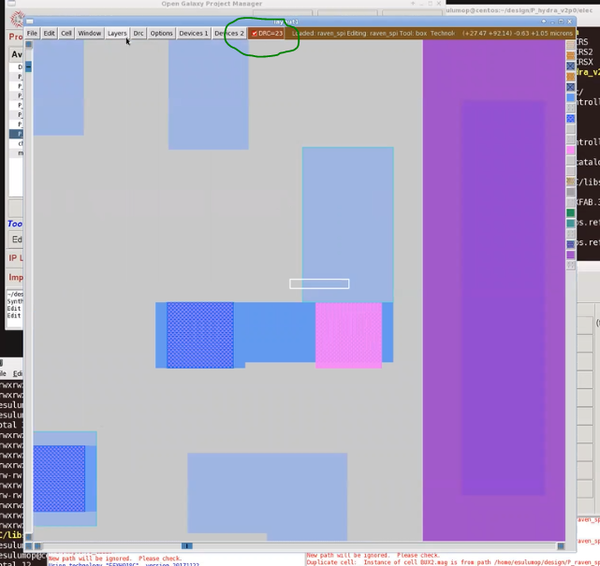

These kind of DRC errors is easy to fix, just by covering that small horizontal edge and that solves this DRC error, and reduces DRC count from 25 to 23. See below image:

In above example, we dealt with tons of notch error. The plan (along with PNR on LIVE design) is to show how we fixed all of them and brought the DRC count to zero. Some of these violations needs loads of manual effort, and that justifies the why DRC engineers are so valuable for a chip closure. It can’t just tape out without them.

To learn and understand more about DRC/LVS and in whole, a LIVE Physical design flow, enroll in below webinar happening in 2 days from now (June 2nd). Here’s the link to enroll:

https://www.vlsisystemdesign.com/upcoming-event/

FYI – We are coming up with something new and something exciting, which will be announced in webinar. Stay tuned in webinar