VSD-HDP : Verilator Verification Environment for RISC-V vector accelerator

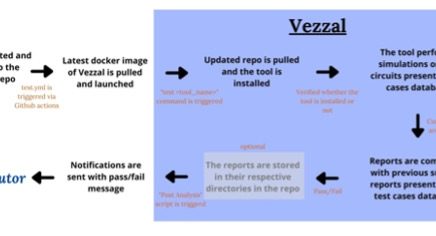

In a nutshell, the project really is to build a Verilator Verification environment i.e. a structure in which we can set up testbenches that are executed with Verilator. The thing which is interesting in this project is we are going to tie that Verilator piece with a golden model arithmetic library and that is going to be something that you can publish as nobody else in the world has that

It’s a Verilator Testbench environment that uses an online arithmetic library to generate the right bit pattern. We are not using randoms, but we are using a Golden model. If you progress from ALU to a vector accelerator, you will have a vector lane, vector register file, vector load/store unit, vector instructions.