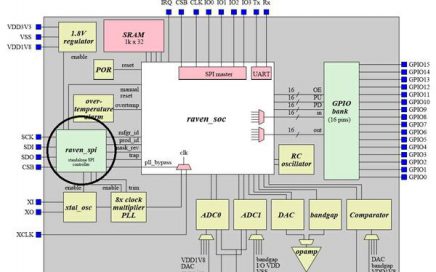

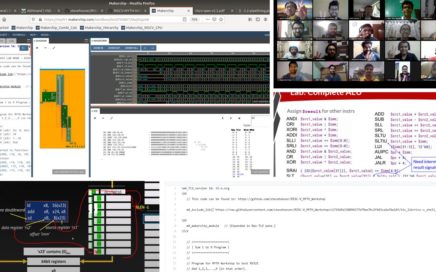

4th mile-stone – 35 RISC-V cores in 5-days – Can you believe it?

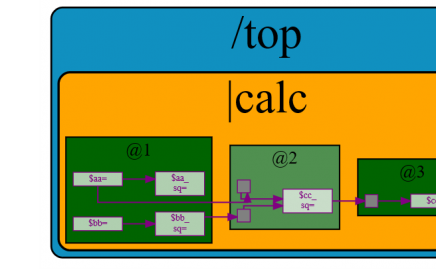

We had Makerchip IDE, TL-Verilog, Day wise Slack channels, Classroom GitHub and VSD-IAT – All of them so seamlessly integrated that every participant followed the loop and there you go. Out of 110 participants, 35 participants built entire basic RISC-V CPU core which is close to 30% participants, and all in 5-days