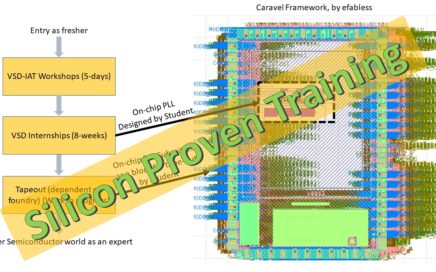

The training, the internship and finally, the tape-out – VSD Silicon proven model

A dream and a mission statement that was framed 10 years back by VSD and efabless (or let us say, e-fabulous) has now taken a […]

A dream and a mission statement that was framed 10 years back by VSD and efabless (or let us say, e-fabulous) has now taken a […]

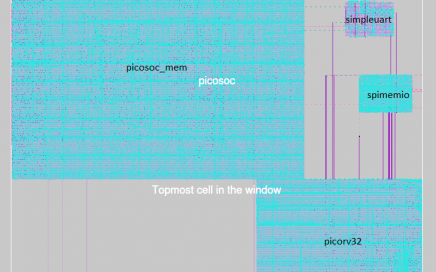

Few months back, I had posted the below floorplan of picoSoC, which is a simple (yet powerful) example of SoC using picoRV32, which can run code directly from SPI flash chip and can be used as a turn-key solution for trivial tasks in ASIC and FPGA designs

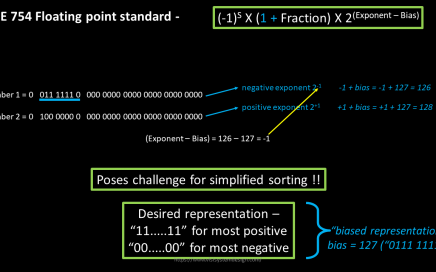

how the IEEE754 floating point standard designed the way it is. Every great design begins with an even better story. We all must have read blogs and watched videos about how to convert a decimal floating-point number to its binary form. We must have seen standard formulas of converting an IEEE754 standard floating-point number to its decimal form.

So glad and happy to let you know that we will be presenting in RISC-V workshop at IIT Madras, India, on July 19, 2018 at 2pm (organized by RISC-V foundation), and topic is something which we have mastered in last 7 years – its about a survey of E31 RISC-V core floorplan and its impact on power, performance and area.

let’s identify what has happened till date in field of EDA/CAD using Machine intelligence. The image below shows the flow diagram for designing a chip. This is what has happened (or happening) in EDA using machine intelligence.