VSDOpen 2019 Demo 1 : Raven Chip – First-time silicon success with Qflow and Efabless

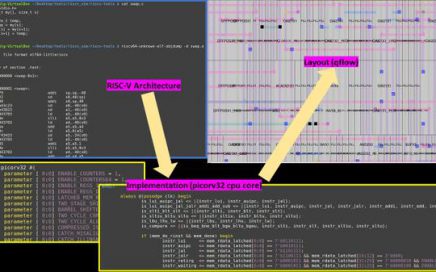

The Raven chip: First-time silicon success with Qflow and Efabless Raven is a open-source top-level SoC design based […]

The Raven chip: First-time silicon success with Qflow and Efabless Raven is a open-source top-level SoC design based […]

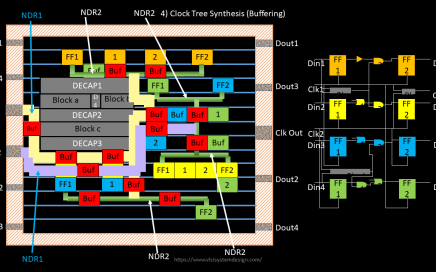

Hey There – Think about it…!! Problem Statement – For hierarchical designs ~500k instance count, participants are expected to develop code which will modify existing […]

Hey There – Think about it!!! Today’s version of open-source EDA tools, work very well for hierarchical designs sub-25k instance count. For hierarchical designs ~500k […]

Hi “Pictures speak it all” Finally, we all did it – VSDOpen – first ever online VLSI conference. Very close to a real one – […]

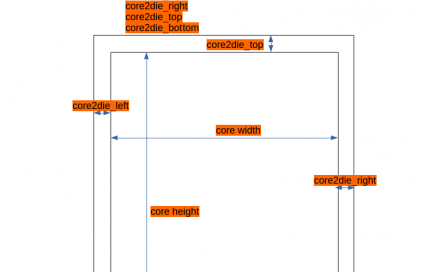

An opensource padframe generator was developed on the efabless platform for usage with the Open-Source Qflow Digital Synthesis Flow, for digital logic chips in the X-FAB XH018, 180nm process.

This paper describes an opensource padframe generator that was developed on the efabless platform for usage with the Open-Source Qflow Digital Synthesis Flow, for digital logic chips in the X-FAB XH018, 180nm process. It is presented by Philipp, who is a software developer with a strong background in security and cryptography. He is currently learning microelectronics.

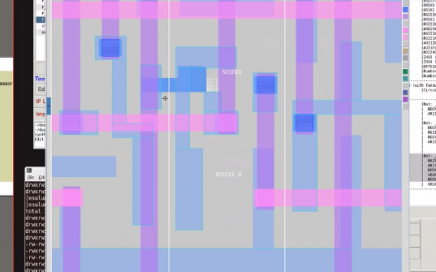

DRC is something which (most likely) is supposed to fail in first instance. Let’s see what you do to fix them. In below eg. drc count is 25. Qrouter (an open-source router, which will be discussed in detail in webinar) is really good with some standard cell sets like the one which comes distributed with qflow, like OSU018, they are really nice one’s to work with. All the ports have nice squares, they don’t have these inside ‘L’ corners as shown below.

A high-level program, like swap.c as shown below is first converted to an assembly language program (RISC-V in below example) using compiler. This assembly language is converted to binary machine language program using an assembler. This level of abstraction of your application using high-level programming languages like C, C++, Java or Visual Basic, proves to be a great idea to improve design