Hello

So now that you get the point of generated clocks in previous Part 1 and Part 2 of this post, now let’s conclude this by waveform derivation, means, suppose you are being given a generated clock table and now you want to derive the clock waveform out of it, how do you do it. Its very very simple if you have gone through my previous posts.

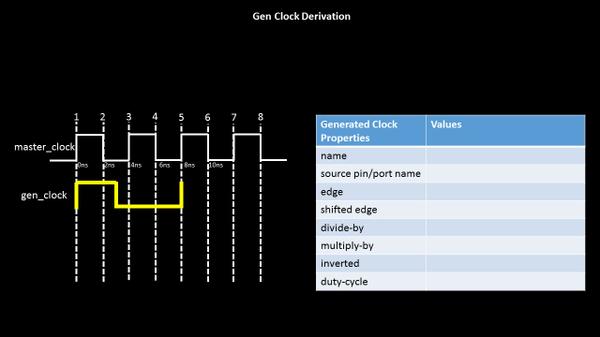

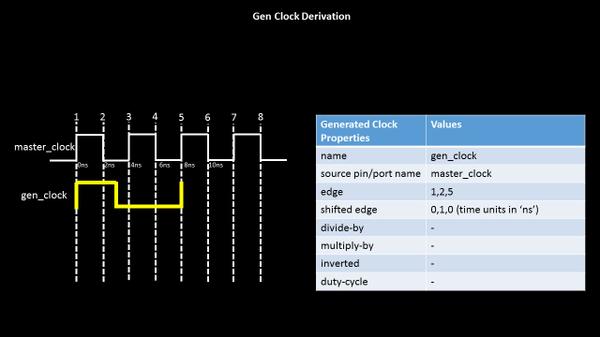

Let’s assume that, and begin with below simple example of waveform table (by the way, this is a very classic interview question in semiconductor industries. Also, this technique is used to debug complex clock constraints in industries)

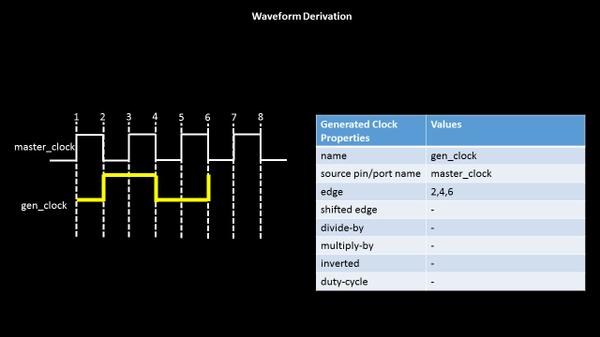

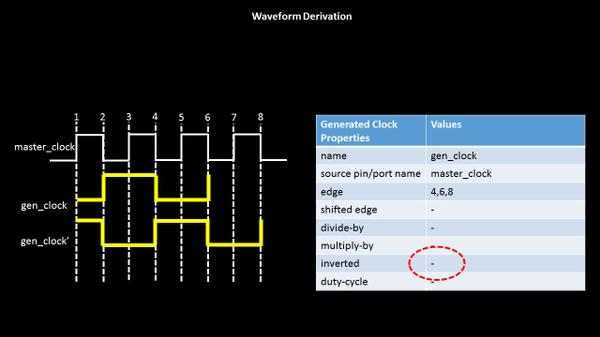

So the above table, says, the first rise edge of the generated clock arrives at 2nd edge of master clock (remember, it doesn’t matter whether 2nd edge of master clock is a rise or fall), the first fall edge of generated clock arrives at 4th edge of master clock and second rise edge comes at 6th edge of master clock and below is how your generated clock will look like

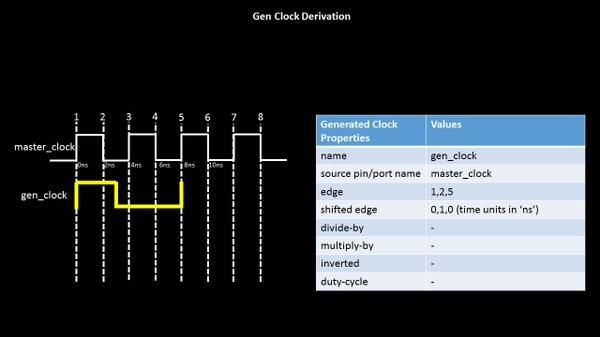

Let’s put this to test. How about everything else in above table remains the same, but the also the inverted is ‘ticked’, then the same gen clock will look something like below. Also, there is a trick that can be done to define the below gen clock. i.e……..(sentence continued after below image)

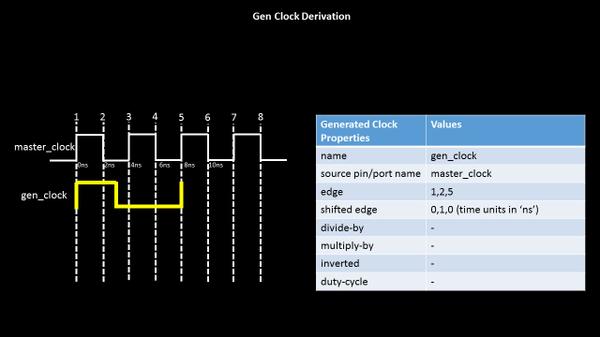

(…sentence continued from above image) the same gen_clock’ can be defined using just the edges, and removing options of the table. And below is how the generated clock definition will look like for gen_clock’

And finally, lets look into a more complex table like below, where we have the generated clock edges coming in middle of clock edges at some ‘t’ time units