150+ students have decided to upskill in VLSI

And that’s where VSD must play an especially important role to bring in latest and greatest VLSI skills to you, atleast in the field of open-source hardware. VSD owes a lot to VLSI community and hence has planned 3 exclusive cloud lab-based VLSI workshops on 3 important topics, with top 3 expert instructors from around globe, having more than 2 decades of experience – Tim Edwards, Steve Hoover, and Prof. Mohamed Shalan

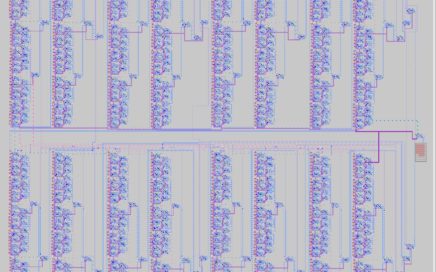

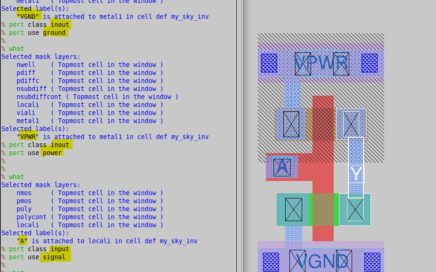

Open-source EDA tool development with lab exercises using Sky130 pdk’s by Google/Skywater

RISC-V micro-architecture using transaction level – Verilog with lab exercises on Makerchip Platform

SoC and Physical Design using Automated RTL2GDS OpenLANE tool with lab exercises using demo design and Sky130 pdk’s.