Paper 2: PNR for digital core IC to pads using Cloud based eda tool

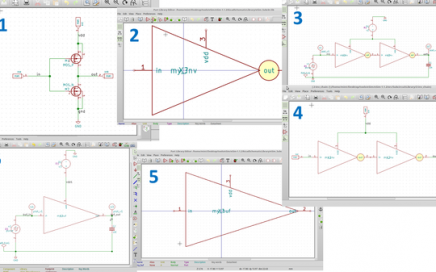

A simple chip frequency divider but most prominently used in counter modules of a microproceesor or as standalone IC can be completely designed from Verilog code to layout . A complete chip with IO pins and labels on it can be designed with help of efabless cloud based eda tool just like a commercial IC. There are two toolbox in efabless one is CloudV for Verilog or c code & other is Open Galaxy for backend design for designing commercial like IC with zero cost involved & same can be given to Semiconductor foundries for mass production. From Preparation , synthesis to DRC cleanup using Q flow manager a Core part of IC can be obtained with log files of each stage used in this process. A innovative feature of interactive DRC under Magic tool enables the designer to rectify DRC violations on the spot. Moreover, ESD protection is also available under Opengalaxy tool for use of chip in electrosensitive applications.