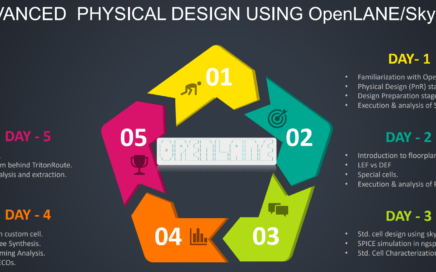

Ever heard of Chip Design Pentagon?

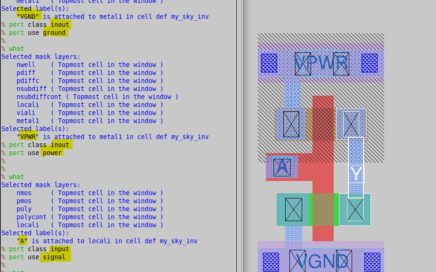

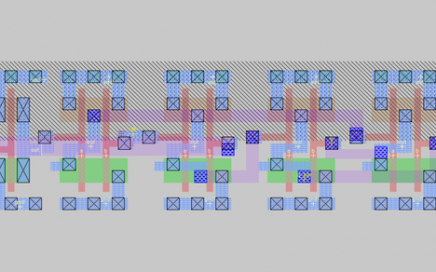

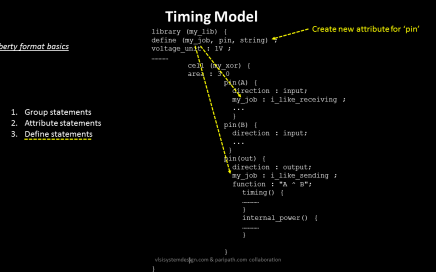

Know what Pentagon is? It is a plane figure which has 5-straight sides and 5-angles. For a perfect pentagon, it needs all its sides and angles to be the same, till the last decimal. Do you know what is the similarity between pentagon and our upcoming workshop “Advanced Physical Design workshop using OpenLANE/SKY130”? Look above image and you would guess it right. It is a perfect blend of topics where even a fresher can jump-start his/her career in chip design in just 5-days