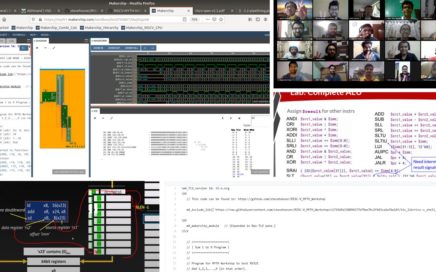

5th mile-stone in field of open-source – another compact SRAM

This time its @Reuel did a pretty great job of building a pretty compact 6T-SRAM cell and he is just a third year engineering student

This time its @Reuel did a pretty great job of building a pretty compact 6T-SRAM cell and he is just a third year engineering student

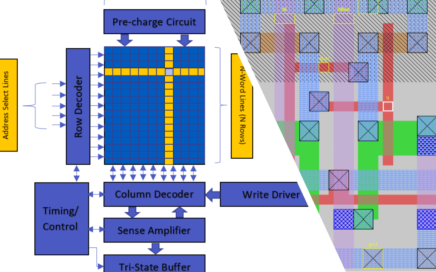

We had Makerchip IDE, TL-Verilog, Day wise Slack channels, Classroom GitHub and VSD-IAT – All of them so seamlessly integrated that every participant followed the loop and there you go. Out of 110 participants, 35 participants built entire basic RISC-V CPU core which is close to 30% participants, and all in 5-days

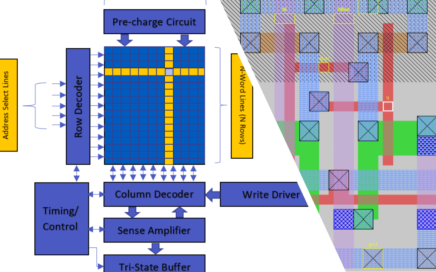

@Yash joined our research project group under VSD Research internship program which runs for 8-weeks. He was supposed to explore openRAM memory compiler flow, develop all custom cells required by openRAM using OSU180nm and generate 4kB SRAM with an access time of 2.5ns

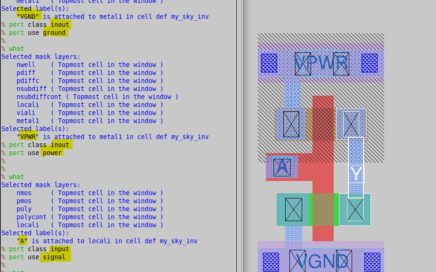

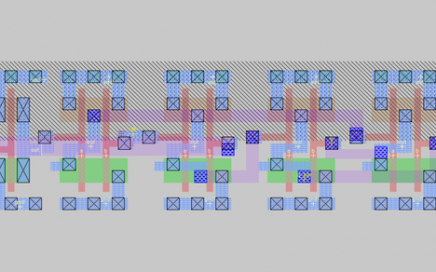

@Nickson joined our research project group under VSD Research internship program which runs for 8-weeks. He was supposed to develop flow for standard cell design and characterization using all open-source tools – magic/ngspice, then plug those standard cells into open-source PNR flow by open-lane, and benchmark RTL2GDS flow results. This needed a knowledge, not only of PNR, but device physics, custom layout, DRC/LVS and then (finally) Physical design/STA.

GitHub is the new Resume for VLSI industry

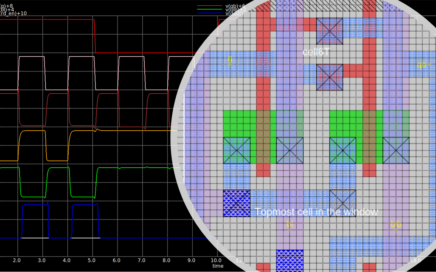

Power rail discontinuity – We would like to have continuous power rail.N- and P-diffusion discontinuity – We would like to have continuous diffusion. For my Physical design friends, remember, we add “FILLER” cells at the end of routing, and you always wondered why we are doing so.Small substrate contacts – Except for inverter, all substrate contacts are single width, which will create high resistance path for current, thus increasing “Clk-to-Q” delay.Hanging metal1 – If you see for the NAND gate outputs, there is lot of hanging metal1.

With learning being online, SHAKTI core and ‘vsdflow’ being opensource, this is first-time in the history of VLSI design & EDA (thanks to RISC-V ecosystem and Shakti Team at IITM lead by Prof. Kamakoti), a chip will ever be taped-out using all open source flow, which will cater to almost 80% Indian Semiconductor Market.

It wasn’t that bigger deal for Intel because they thought, at the time, it will be 250,000 chips will be sold for 5 years, which isn’t that many. But they were wrong. It was a 100Million computers were sold. And suddenly 8086 from being an emergency back-up was an over-night success and had a very bright future, because it was binary compatible of PC software, and so had great opportunity

Isn’t that an inspiring story?

Hi Vlsi

Your feedback has been continuously pushing us to the edge. And I really want to Thank You for all the support you have been giving over the past. Its due to this push, we are now releasing (especially for VLSI freshers), a package, which you just need to download/run. That would install all opensource EDA tools on your UNIX machine plus run a complete RTL-2-GDS on RISC-V core ‘picorv32’.

All you need to do is go to below github link, and follow simple 5 steps given in the README of below link:

In last 50 years, there are 3 lessons that we can draw. First – software advances can inspire architecture innovations. Second – when we raise the hardware/software interface, it creates opportunities for architecture innovation. Third – in our field, the way we settle these debates, isn’t by just arguing in a bar, rather people spent/invest billions of dollars to investigate their ideas and marketplace settles these debates