Hey There,

Of-course there is a requirement for open-source verification, but that’s not the only thing we want to cater to. There are other verification trends and challenges which system verilog and other verification platforms are not able to meet. So, we want to position Embedded-UVM for that

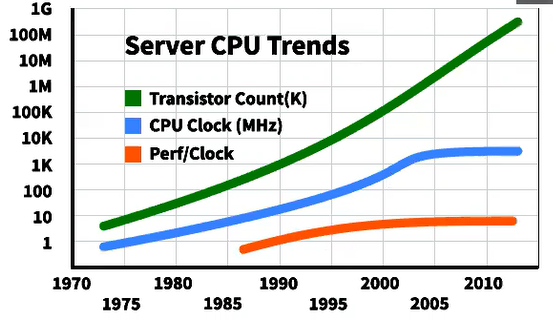

In the past decade or so, the major thing which is making verification tougher than it used to be, is the death of Moore’s law

As far as processor frequency goes, it stabilizes at 4GHz and its coming down as we move to multi-core processors. So, when you look at it from simulation perspective, post 2005 it is becoming increasingly difficult to run simulations on bigger chips.

Chip size keeps increasing, while processor speed is stagnant and hence, simulation is a limiting factor. Simulation speed is going to be limited unless we move to multi-core processors

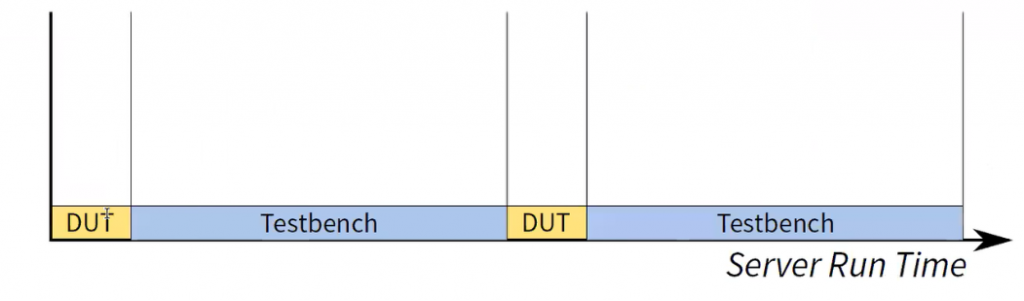

Contemporary EDA tools runs RTL simulations in multi-core environment. System Verilog doesn’t run in multi-core environment.

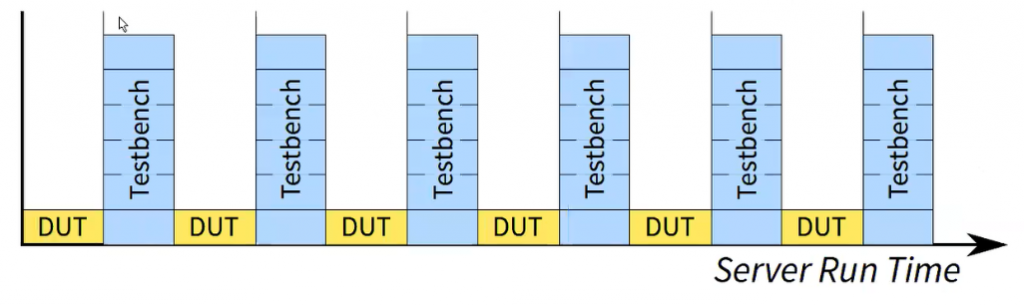

Therefore, test-bench runs on one thread and RTL runs on multiple threads. RTL is more formal in nature, in sense, it can be synthesized, it can be partitioned, different partitions can run on different processors, while testbench is behavioral in nature and it cannot be partitioned the way RTL can be

So how do we move from below….

……to below??

Stay tuned to below link for upcoming webinar on “Opensource Verification and Emulation using Embedded-UVM”