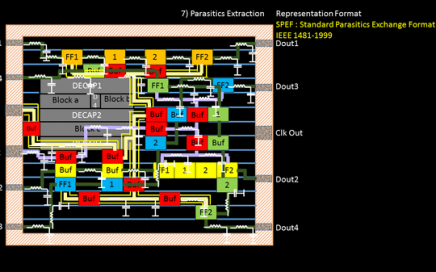

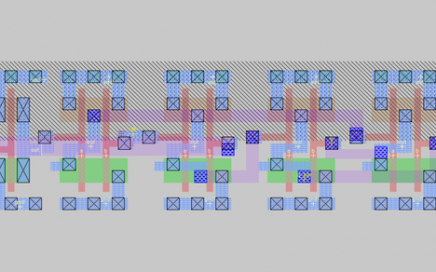

The horrible std cell ever designed by me….

Power rail discontinuity – We would like to have continuous power rail.N- and P-diffusion discontinuity – We would like to have continuous diffusion. For my Physical design friends, remember, we add “FILLER” cells at the end of routing, and you always wondered why we are doing so.Small substrate contacts – Except for inverter, all substrate contacts are single width, which will create high resistance path for current, thus increasing “Clk-to-Q” delay.Hanging metal1 – If you see for the NAND gate outputs, there is lot of hanging metal1.