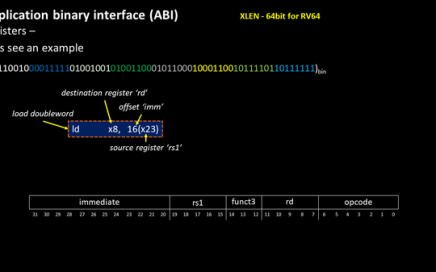

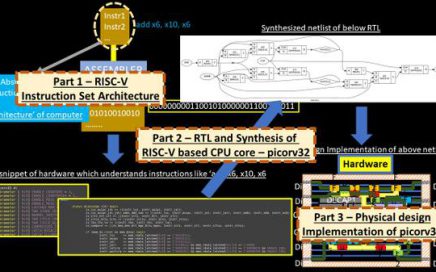

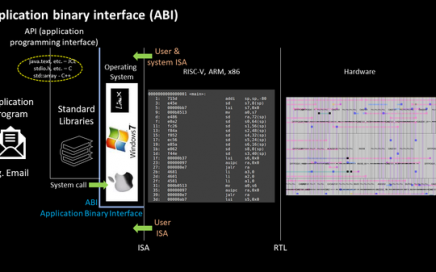

ABI – Get this one right – RISC-V is all yours..

ABI (application binary interface), as the name says, is an interface, that helps programs access system hardware and services.RISC-V architecture has 32 registers (we explained, in detail, why this architecture has 32 registers in our online course). Application programmer, can access each of these 32 registers through its ABI name, for example, you need know the value of stack pointer or move the stack pointer, all you need to do is “addi sp, sp, -16”, where ‘sp’ is the ABI name of stack pointer.