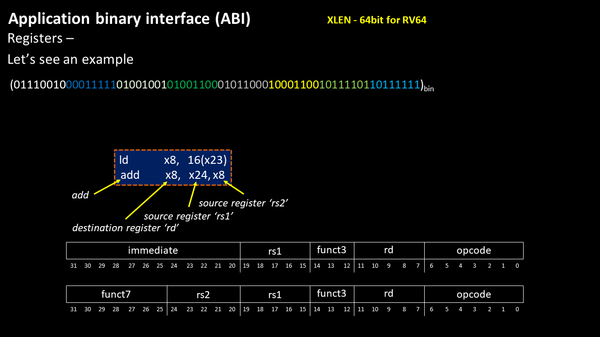

Another example, shown below, adds contents of x8 with data present in x24 and stores results back in x8. Here, we have 2 source registers x24 and x8, and one destination register x8

Again, focus at ‘rd’, ‘rs1’ and ‘rs2’. They are all 5 bits, which means, to represent x24 in rs1, that field will contain ‘11000’

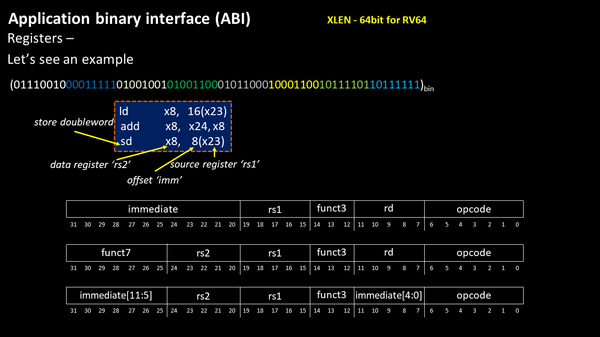

One is good, two is better, three is best…So let’s look into third example below

In the example, the contents or ‘x8’ are stored in memory whose base address is present in register ‘rs2’ and offset is ‘8’

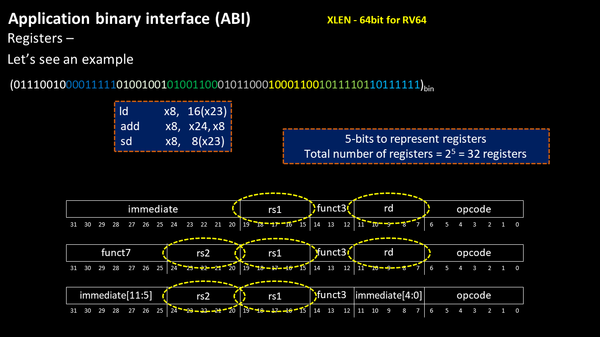

Once more, focus on ‘rs2’ and ‘rs1’. They are again 5 bits. Practically, to keep design simple, all registers in a RISC-V architecture is represented by 5-bit binary pattern.

The good part has already been per-launched and best part is yet to come.

The reason we launched this course, is because, we were asked to come with a design, which we can take through the entire RTL-synthesis-PNR-STA tool chain and after a lot of thought, we believed that understanding a sophisticated RISC-V CPU core is the best way to learn how to write specs, how to implement and how to PNR…all in one…

Stay tuned, more exciting things yet to come…

Till then…happy learning…