History etched with VSDOpen2018 – First VLSI online conference….

Hi “Pictures speak it all” Finally, we all did it – VSDOpen – first ever online VLSI conference. Very close to a real one – […]

Hi “Pictures speak it all” Finally, we all did it – VSDOpen – first ever online VLSI conference. Very close to a real one – […]

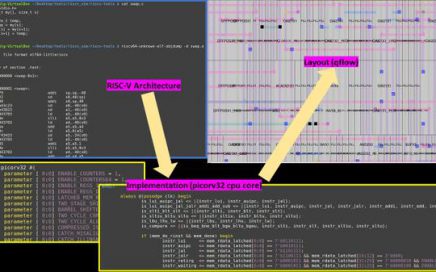

This paper introduces TL-V erilog and W ARP-V and then describes the formal verification of WARP-V using riscv-formal, a formal verification framework for RISC-V. Timing-abstraction and transaction-level design are showing significant benefits for hardware modeling, but this is the first demonstration of their benefits for verification modeling. As evidence of these benefits, the verification of all RISC-V configurations of WARP-V is accomplished in a single page of code.

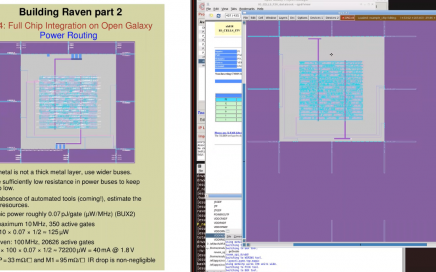

This blog is regarding abstract submission for VSDOpen2018, which is the first online conference in VLSI, that covers all aspects of semiconductor technology with prime focus to build SoC using RISC-V CPU by illustrating exciting ways using (only) opensource EDA tools.

A high-level program, like swap.c as shown below is first converted to an assembly language program (RISC-V in below example) using compiler. This assembly language is converted to binary machine language program using an assembler. This level of abstraction of your application using high-level programming languages like C, C++, Java or Visual Basic, proves to be a great idea to improve design