Hello

First of all, I would like to ‘Thank You’ all for the messages/doubts that you have sent me over linkedin, [email protected], facebook, etc.

Really overwhelmed by the responses on my previous post. But not sure, whether you all know, we already have an online course on Signal Integrity, that’s a one-stop shop for all your queries and messages.

I have covered (almost) all topics which are expected while working towards signal integrity issues on chips. Just click on the link provided at the end of this post.

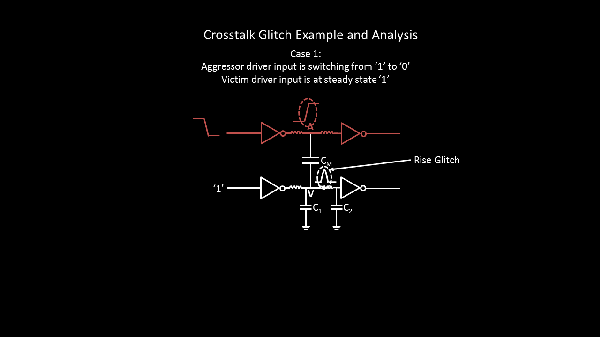

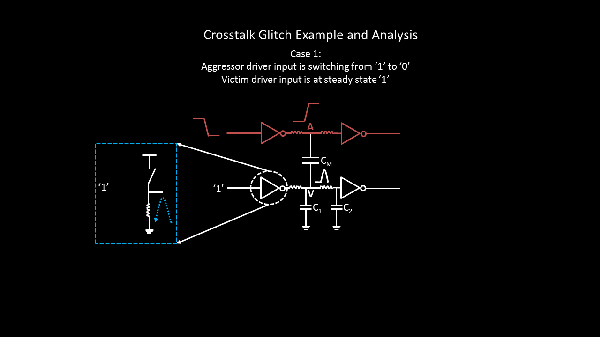

Coming back, we saw the below rise glitch

The big question… Is this glitch really harmful or will it die out as it progresses through the next inverter connected to it?

Let’s come back to this question in some time. For now, let’s analyze this glitch even more. Let’s see, if there’s any catch. Let’s do some smart work here 🙂

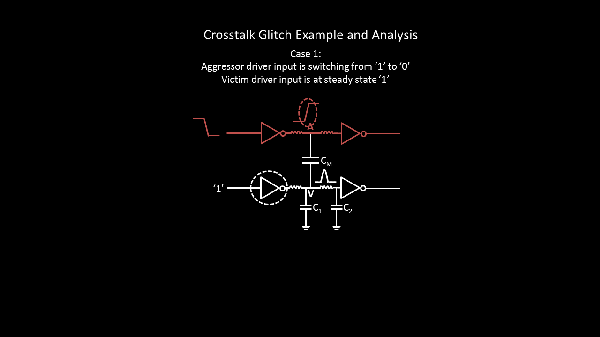

Have a close look at the inverter just before this glitch

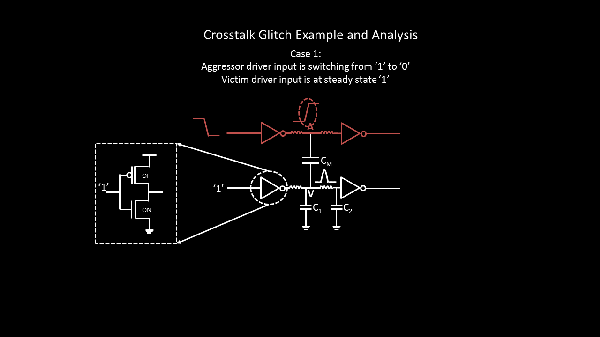

And derive the current position of the inverter below, using PMOS/NMOS/Resistance/Capacitance.. (I really love to go to that deep level).

Also, very soon, after you go through all my online lectures/posts, you will realize, its these MOSFET’s and its internal resistances and capacitance, that build the $Billion VLSI world and drive VLSI industries

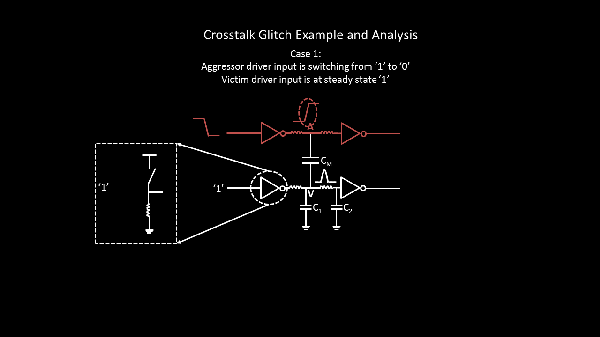

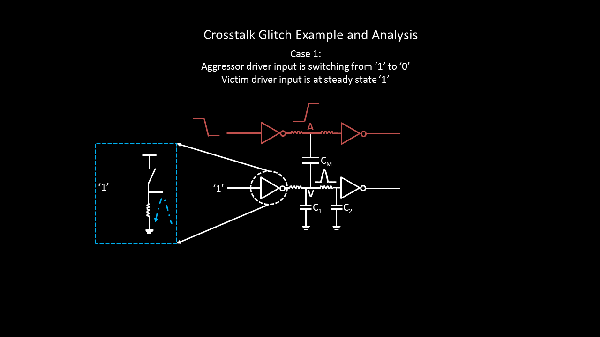

The off PMOS can be replaced by an open switch and on NMOS can be replaced by a resistance like below

In the above case, the inverter (NMOS specifically) was able to discharge the glitch completely, thus making this one as a ‘safe glitch’..

And just now, I introduced you to 2 new things …. 1) a way to reduce glitch, and 2) the term ‘safe glitch’..

I think I should leave you here to ‘think’, on these 2 things 🙂 And, may be, after reading this post, you actually solved one glitch issue at your work place OR may be answered an important question related to glitch in your interview. These are some tricky questions.

“An artist is an explorer. He should begin by seeking himself, seeing himself act. Then, not restraining itself. And above all, not being easily satisfied.” –Henri Matisse

So, EXPLORE, what I just introduced :). I will be anyways coming back on these topics in my next post

Thanks

Kunal