Hi Everyone,

My name is ‘Reset Synchronizer’. I have been tasked to do a very specific job. Though, I look to be a very small piece of circuit, I help the whole design to get rested without any violations. You can think of my job to be very similar and as critical as my brother ‘The clock’. Even I my own tree and my own network, just like my brother has. The only difference is, I am not as strict on skew, as my brother is. I am a bit flexible, which makes me even prouder and lovable by designers 🙂

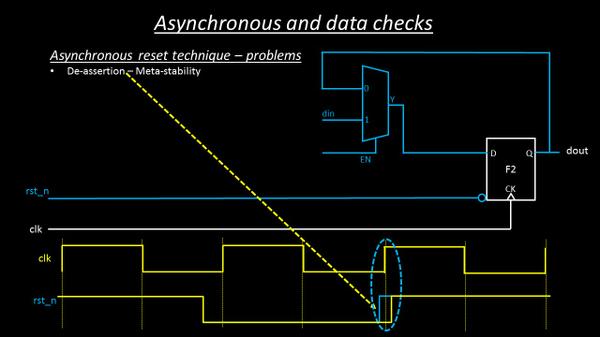

Let me try to show you in below image, what happens when you try to reset design without me, asynchronously

My close friend (also the one who can’t stay without me, stay with me till end of this post) ‘rst_n’ looks to be very confident while asserting himself onto whole design and very successfully resets the complete design. But he creates lots of problems for the whole design, while de-asserting himself. How? Whenever he tries to de-assert himself near active edge of clock, he creates violations, doesn’t satisfy setup/hold requirements of flops, corrupts their data and creates meta-stability

That’s when, these flops, came to me asking for a solution. I gave it a lot of thought, and tried to convince my friend ‘rst_n’ to allow me come and stand firmly in between him and the design. He’s my friend, and so I should be saving him, right. I mean, that’s friends are for….

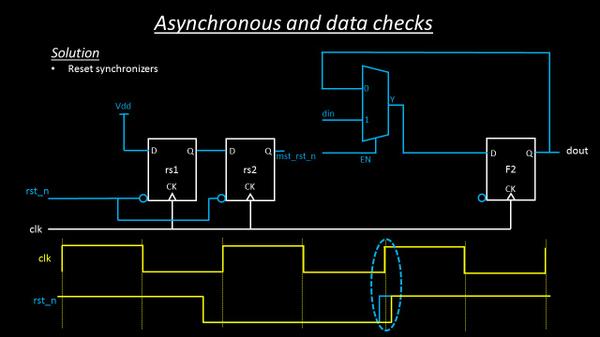

So I came in between, like shown in below image….

Now, I have a very superior connection, with Vdd directly connecting me at my ‘D’ input and my friend ‘rst_n’ connecting with me at my ‘RST’ pin.

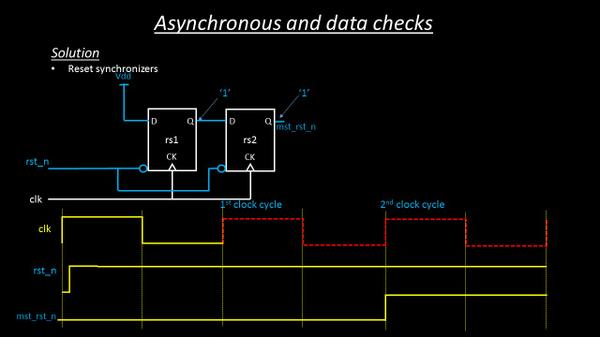

Now, I ask my friend ‘rst_n’ to first reset me, so that I go to a ‘0’ state, and then first de-assert me, so that only I corrupt my data (which is ok for me). My connections are so strong (see the second flop rs2), that I can easily overcome my meta-stability in 2 clock cycles as shown below:

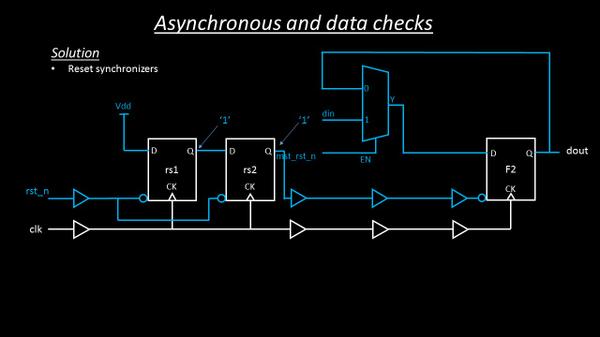

Not only that, I also take forward this ‘mst_rst_n’ signal to all flops in the design, like a tree, just like the clock, as shown in below image. Now that I look just like any reg2reg path, my other friends, flip-flops, should just check me like any other reg2reg setup and hold violation

Since that now I am being treated with same dignity and respect that my brother ‘The clock’ is being treated, the violations produced due to my signal ‘mst_rst_n’ is being given a special name. I am not called setup or hold violation, I am being called as the proud ‘reset recovery’ and reset removal’ violations.

From the above whole scenario, I have learnt one major thing in my life which is being very well composed as below quote by ‘Katrina Mayer’:

“Even a small act of kindness can make a big difference in someone’s world”

Do one small act of kindness today …. Register in my courses 🙂