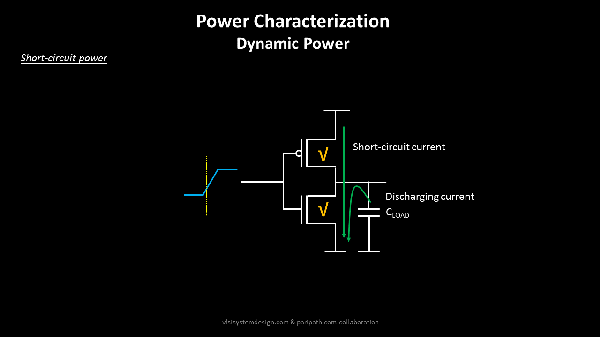

When your input is at logic ‘0’ and assuming your VDD is at 1.8V (considering it’s a 180nm technology node), why do you think, from physics point of view, does your PMOS turns ON? The reason is, logic ‘0’ at gate means its at 0V, Vdd is at 1.8V, the PMOS Vgs = 0 – 1.8 = -1.8v which is far above the threshold voltage of PMOS transistor, which makes the PMOS to turn ON

Similarly, Vgs of NMOS is 0V – 0V = 0V, which is below the threshold voltage of NMOS transistor and hence NMOS is OFF. Now look at the highlighted area in the input transitioning waveform. In that area, if gate input rises from 0v to (say) 0.5v, the Vgs of NMOS is 0.5v, which is just above the threshold voltage of NMOS (assuming NMOS Vt is 0.2V for 180nm technology node), so it just turns ON

Now the Vgs of PMOS is roughly, say 0.5v – 1.8v = -1.3V which is again, far above threshold voltage of PMOS transistor, so your PMOS transistor is still ON. You see, at this point, both PMOS and NMOS transistor are ON. Looking Vdd at higher potential, and GND at lower potential, there is now a direct path from Vdd to Gnd.

That’s short circuit current, and hence the name short-circuits power dissipation

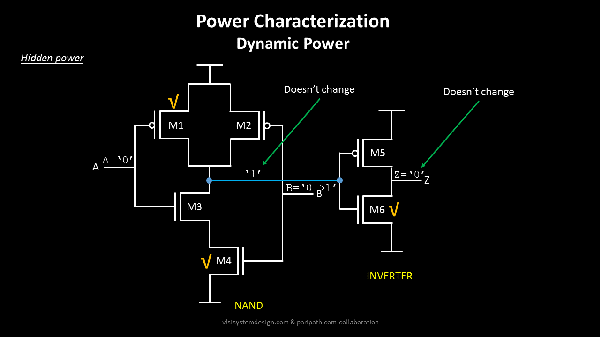

So now the big question? What if the outputs do not switch, while only the inputs switch, like the below case of AND gate

Here, if you see, even though your input ‘B’ switches from logic ‘0’ to logic ‘1’, your NAND output and hence, the AND output doesn’t switch. So do we still see power dissipation in these kind of scenarios?

Hidden power

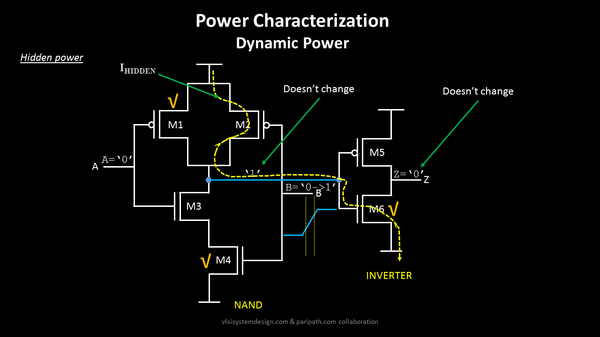

That’s me…”hidden power”. That’s how I introduced myself in the beginning of the post. Now even though, in the above image, the outputs do not switch, the switching of input ‘B’ creates a unique path for current flow from Vdd to Gnd. Look at below image:

During the transitioning of ‘B’, due to similar reasons of Vgs being greater than threshold voltage of PMOS and NMOS transistors, M2 is ON momentarily, and I flow from Vdd – M2 – M6 – GND. Since I am hidden inside the boundary of the cell, the name hidden power

This brings me to very important point about myself, that if I am hidden, doesn’t mean I do not exist…

“Language exerts hidden power, like the moon on the tides” – Rita Mae Brown

Happy Learning !!