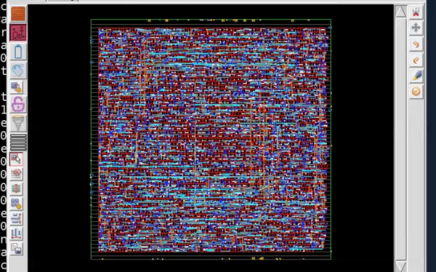

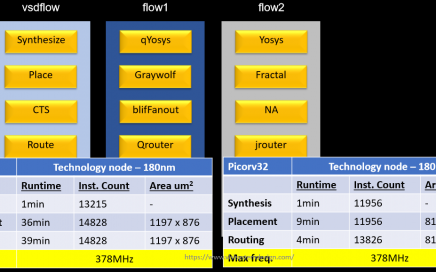

Symposium IV – Place and route of digital IC’s for best PPA

A good takeaway from above is which is the best flow – Well, there is no single answer to this. You can use “flow 1”, if your organization is constrained by cost and comparable performance, and you can go for “flow 2” if performance is the criteria.