VSDSquadron

Unlock "Exclusive lifetime Access to a comprehensive 40-hour lab intensive module covering RISC-V, VLSI Physical Design, Static Timing Analysis and CMOS Circuit Design"

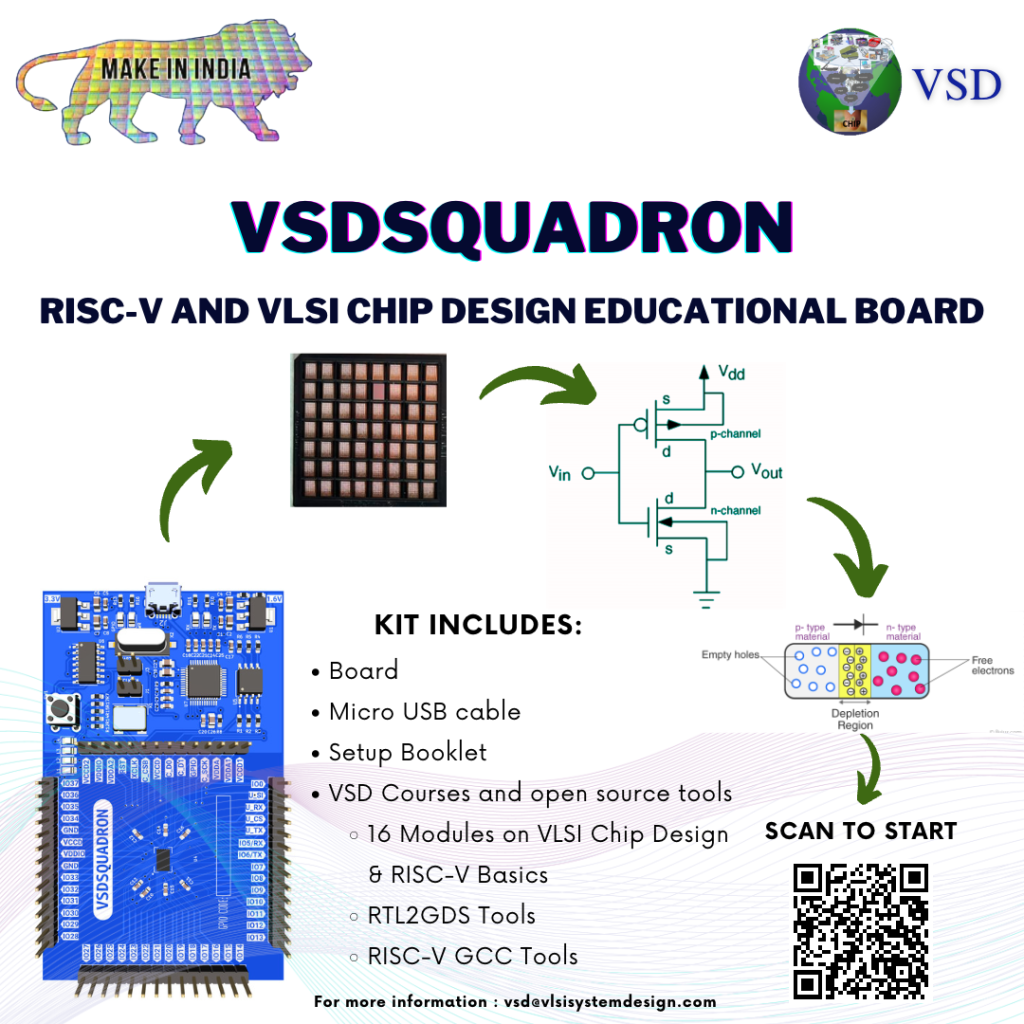

VSDSquadron, a cutting-edge development board based on the RISC-V architecture that is fully open-source. This board presents an exceptional opportunity for individuals to learn about RISC-V and VLSI chip design utilizing only open-source tools, starting from the RTL and extending all the way to the GDSII. The possibilities for learning and advancement with this technology are limitless.

Furthermore, the RISC-V chips on these boards should be open for VLSI chip design learning, allowing you to explore PNR, standard cells, and layout design. And guess what? vsdsquadron is the perfect solution for all your needs! With its comprehensive documentation and scalable labs, thousands of students can learn and grow together.The vsdsquadron is an educational kit with general-purpose interfaces that enables you to evaluate features of RISC-V ISA.

VSDSquadron Datasheet

Kit includes

VSDSquadron Kit :

Get lifetime access to RISC-V Programming and VLSI Chip Design industry grade educational content with the Kit

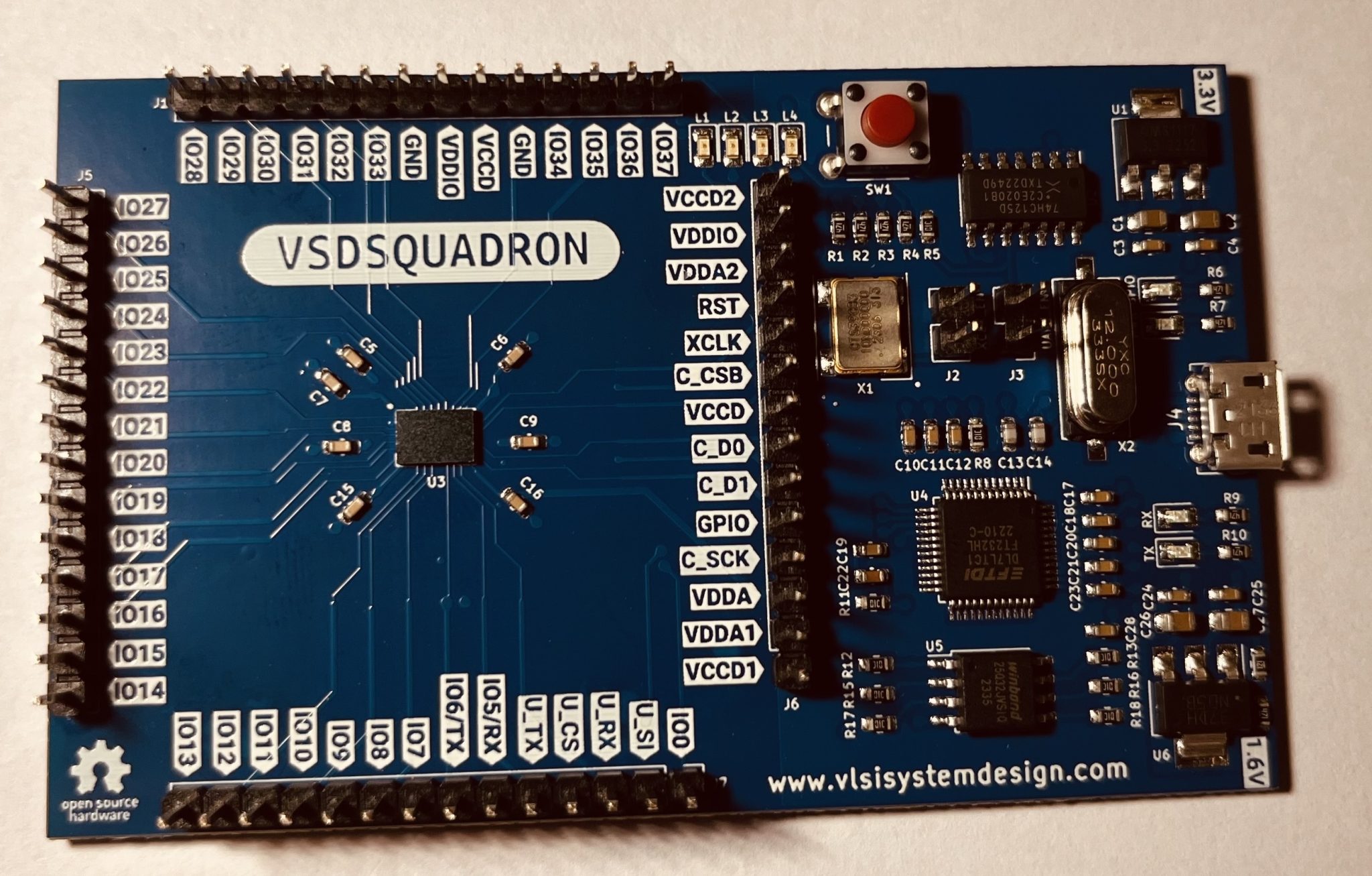

If you're interested in learning about RISC-V programming and VLSI Chip design, then you're in the right place! We are thrilled to announce the release of our brand new vsdsquadron board, which comes loaded with at least 10 GPIOs that are perfect for a wide range of projects. And that's not all – we're also including a collection of labs and theory modules that are designed to help you get started with RISC-V programming and design.

Our theory modules cover everything you need to know about RISC-V programming and design. You'll start with an introduction to RISC-V ISA and GNU compiler toolchain, learn about integer number representation and arithmetic operations, and even delve into topics like GLS, Synthesis-Simulation mismatch, and blocking/non-blocking statements. Additionally, our circuit design and SPICE simulations modules will teach you the basics of circuit design and SPICE simulations, as well as how to evaluate noise margin robustness and power supply variation robustness.

By pre-ordering now, you'll be one of the first to receive our vsdsquadron board and all the tools you need to start exploring RISC-V programming and VLSI chip design. Whether you're a seasoned professional or just starting out, our labs and theory modules will help you take your skills to the next level. So don't hesitate – place your pre-order today and join the vsdsquadron community!

Board:

The vsdsquadron board comes with a minimum of 10 GPIOs, which makes it ideal for a diverse range of projects. The board specifications are provided here, and a USB cable is included for easy programming, allowing you to start your projects promptly. Additionally, a list of applications that can experiment with on the board are listed below.(Parts used for demo applications are not included in the Kit)

- Line Follower

- 4-digit seven segment

- Servo motor

- IOT and home automation

- And many more

Labs:

Our labs are designed to help you get started with RISC-V programming, synthesis, physical design, and circuit design. We've included pre-compiled packages for all the tools you'll need, including software, PDKs, and more. We recommend using Ubuntu 20.04 or above for best results.

Theory:

We highly recommend using the precompiled tools provided above to run the courses. Using any other version could result in differences with the lecture video content.

- RISC-V Basics

- RTL Design and Synthesis

- Circuit design and SPICE simulations

- Physical Design

VSD Modules and Labs

Modules Name

Chapters

VLSI Ed-Tech Introduction

The Big Picture-Need for RISC-V

Introduction to RISC-V ISA and GNU compiler toolchain

Introduction to RISC-V basic keywords

Labwork for RISC-V software toolchain

Integer number representation

Introduction to ABI and basic verification flow

Application Binary interface (ABI)

Lab work using ABI function calls

Basic verification flow using iverilog

Need for IP design

The Big Picture - IP design Specs to GDS flow

IP design Prerequsite - Basics of NMOS Drain current (Id) vs Drain-to-source Voltage (Vds)

Introduction to Circuit Design and SPICE simulations

NMOS resistive region and saturation region of operation

Introduction to SPICE

IP design Prerequsite - Velocity saturation and basics of CMOS inverter VTC

SPICE simulation for lower nodes and velocity saturation effect

CMOS voltage transfer characteristics (VTC)

IP design Prerequsite - CMOS Switching threshold and dynamic simulations

Voltage transfer characteristics – SPICE simulations

Static behavior evaluation – CMOS inverter robustness – Switching Threshold

IP design Prerequsite - CMOS Noise Margin robustness evaluation

Static behavior evaluation – CMOS inverter robustness – Noise margin

IP design Prerequsite - CMOS power supply and device variation robustness evaluation

Static behavior evaluation – CMOS inverter robustness – Power supply variation

Static behavior evaluation – CMOS inverter robustness – Device variation

Analog IP design example

IP design example using ALIGN Opensource Tool for Analog Circuit Layout Synthesis

Introduction to Macros

The Big Picture - What are Macros?

Introduction to Verilog RTL design and Synthesis

Introduction to open-source simulator iverilog

Labs using iverilog and gtkwave

Labs using Yosys and Sky130 PDKs

Labs using Yosys and Sky130 PDKs

Timing libs, hierarchical vs flat synthesis and efficient flop coding styles

Introduction to timing .libs

Hierarchical vs Flat Synthesis

Various Flop Coding Styles and optimization

Combinational and sequential optmizations

Introduction to optimizations

Combinational logic optimizations

Sequential logic optimizations

Sequential optimzations for unused outputs

GLS, blocking vs non-blocking and Synthesis-Simulation mismatch

GLS, Synthesis-Simulation mismatch and Blocking/Non-blocking statements

Labs on GLS and Synthesis-Simulation Mismatch

Labs on synth-sim mismatch for blocking statement

Inception of open-source EDA, OpenLANE and Sky130 PDK

How to talk to computers

SoC design and OpenLANE

Get familiar to open-source EDA tools

Good floorplan vs bad floorplan and introduction to library cells

Chip Floor planning considerations

Library Binding and Placement

Cell design and characterization flows

General timing characterization parameters

Design library cell using Magic Layout and ngspice characterization

Labs for CMOS inverter ngspice simulations

Inception of Layout – CMOS fabrication process

Sky130 Tech File Labs

Pre-layout timing analysis and importance of good clock tree

Timing modelling using delay tables

Timing analysis with ideal clocks using openSTA

Clock tree synthesis TritonCTS and signal integrity

Timing analysis with real clocks using openSTA

Final steps for RTL2GDS using tritonRoute and openSTA

Routing and design rule check (DRC)

Power Distribution Network and routing

TritonRoute Features

Mixed Signal SoC Design and Full Chip RTL2GDS

The Big Picture - SoC Design

Mixed-signal full chip SoC design and implementation

Project Work - Chip Testing planning

The Big Picture - vsdsquadron board planning and verification

Caravel Chip Details

RISC-V summary

VSDSquadron firmware

VSDSquadron FT232 and Flash Operation

VSDSquadron Reset Flow and Boot Process

Project Work -Using “VSDSqaudron” development of RISC-V application

Coming up

Modules Name | Chapters |

VLSI Ed-Tech Introduction | The Big Picture-Need for RISC-V |

Introduction to RISC-V ISA and GNU compiler toolchain | Introduction to RISC-V basic keywords |

Labwork for RISC-V software toolchain | |

Integer number representation | |

Introduction to ABI and basic verification flow | Application Binary interface (ABI) |

Lab work using ABI function calls | |

Basic verification flow using iverilog | |

Need for IP design | The Big Picture - IP design Specs to GDS flow |

IP design Prerequsite - Basics of NMOS Drain current (Id) vs Drain-to-source Voltage (Vds) | Introduction to Circuit Design and SPICE simulations |

NMOS resistive region and saturation region of operation | |

Introduction to SPICE | |

IP design Prerequsite - Velocity saturation and basics of CMOS inverter VTC | SPICE simulation for lower nodes and velocity saturation effect |

CMOS voltage transfer characteristics (VTC) | |

IP design Prerequsite - CMOS Switching threshold and dynamic simulations | Voltage transfer characteristics – SPICE simulations |

Static behavior evaluation – CMOS inverter robustness – Switching Threshold | |

IP design Prerequsite - CMOS Noise Margin robustness evaluation | Static behavior evaluation – CMOS inverter robustness – Noise margin |

IP design Prerequsite - CMOS power supply and device variation robustness evaluation | Static behavior evaluation – CMOS inverter robustness – Power supply variation |

Static behavior evaluation – CMOS inverter robustness – Device variation | |

Analog IP design example | IP design example using ALIGN Opensource Tool for Analog Circuit Layout Synthesis |

Introduction to Macros | The Big Picture - What are Macros? |

Introduction to Verilog RTL design and Synthesis | Introduction to open-source simulator iverilog |

Labs using iverilog and gtkwave | |

Labs using Yosys and Sky130 PDKs | |

Labs using Yosys and Sky130 PDKs | |

Timing libs, hierarchical vs flat synthesis and efficient flop coding styles | Introduction to timing .libs |

Hierarchical vs Flat Synthesis | |

Various Flop Coding Styles and optimization | |

Combinational and sequential optmizations | Introduction to optimizations |

Combinational logic optimizations | |

Sequential logic optimizations | |

Sequential optimzations for unused outputs | |

GLS, blocking vs non-blocking and Synthesis-Simulation mismatch | GLS, Synthesis-Simulation mismatch and Blocking/Non-blocking statements |

Labs on GLS and Synthesis-Simulation Mismatch | |

Labs on synth-sim mismatch for blocking statement | |

Inception of open-source EDA, OpenLANE and Sky130 PDK | How to talk to computers |

SoC design and OpenLANE | |

Get familiar to open-source EDA tools | |

Good floorplan vs bad floorplan and introduction to library cells | Chip Floor planning considerations |

Library Binding and Placement | |

Cell design and characterization flows | |

General timing characterization parameters | |

Design library cell using Magic Layout and ngspice characterization | Labs for CMOS inverter ngspice simulations |

Inception of Layout – CMOS fabrication process | |

Sky130 Tech File Labs | |

Pre-layout timing analysis and importance of good clock tree | Timing modelling using delay tables |

Timing analysis with ideal clocks using openSTA | |

Clock tree synthesis TritonCTS and signal integrity | |

Timing analysis with real clocks using openSTA | |

Final steps for RTL2GDS using tritonRoute and openSTA | Routing and design rule check (DRC) |

Power Distribution Network and routing | |

TritonRoute Features | |

Mixed Signal SoC Design and Full Chip RTL2GDS | The Big Picture - SoC Design |

Mixed-signal full chip SoC design and implementation | |

Project Work - Chip Testing planning | The Big Picture - vsdsquadron board planning and verification |

Caravel Chip Details | |

RISC-V summary | |

VSDSquadron firmware | |

VSDSquadron FT232 and Flash Operation | |

VSDSquadron Reset Flow and Boot Process | |

Project Work -Using “VSDSqaudron” development of RISC-V application | Coming up |

In summary, by ordering the VSDSquadron board you will grab an opportunity to start exploring Semiconductor career by learning RISC-V programming and VLSI chip design.

Shipping & Refund Policy

Shipping Policies

- To ensure that your order reaches you in the fastest time and in good condition, we only ship via EMS Speed Post and ShipRocket.

- If you believe that the product is not in good condition, or if the packaging is tampered with or damaged, before accepting delivery of the goods, please refuse to take delivery of the package, and Contact us (91-8548037643), mentioning your order reference number. We shall make our best efforts to ensure that a replacement delivery is made to you at the earliest.

- Please note all items will be shipped with an invoice mentioning the price, as per Indian Tax Regulations.

Canceling An Order:

- You can cancel your order before __________.

- Also Order cancellation may attract 5% bank charges depending on the payment methods used by customer.(It is because most of payment gateway providers collect their Commision even though order cancelled and refunded.).

- Due to the nature of the products we are selling and our strict quality policy, we are unable to offer order cancellation and return without valid reason.

100% Refund/Replacement:

- We guarantee to provide accurate descriptions and high quality product as mentioned in the website. In order to protect customers from shipping damage, item mismatch or parts missing etc., we are providing 24 hours time (From the date of order delivery) to report the complaint by email at contactvsd@vlsisystemdesign.com

- Our technical team will verify the submitted details visually and will issue new Kit. Once we received the Kit our experts will verify the issue reported and will send the replacement items to the customer shipping cost prepaid by us.In case, we do not have the kit in stock to provide replacement, we will issue 100% refund.

- Furthermore, no warranty will apply if the Product has been subject to misuse, static discharge, neglect, accident, modification, or has been soldered or altered in any way.

- Due to the nature of the products we are selling and our strict quality policy, we are unable to offer order cancellation and return without valid reason.

Limits Of Responsibility:

We accept no responsibility for improper installation of our products. Electrical polarity must be properly observed in hooking up electrical components.

Media Launch

VSDSquadron was launched by Prof.V.Kamakoti, Director of IIT Madras in "RISC-V Roadshow on SHAKTI Ideology" and was also covered by Media on 27th April 2023