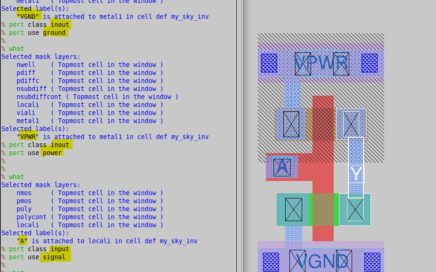

2nd mile-stone in field open-source (open-lane EDA + Google/Sky130)

@Nickson joined our research project group under VSD Research internship program which runs for 8-weeks. He was supposed to develop flow for standard cell design and characterization using all open-source tools – magic/ngspice, then plug those standard cells into open-source PNR flow by open-lane, and benchmark RTL2GDS flow results. This needed a knowledge, not only of PNR, but device physics, custom layout, DRC/LVS and then (finally) Physical design/STA.