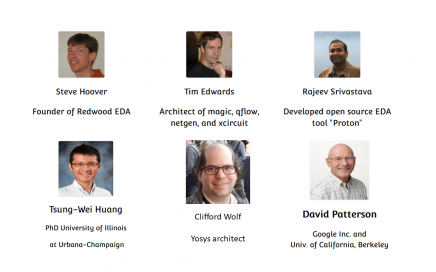

A tribute to opensource (EDA and ISA)

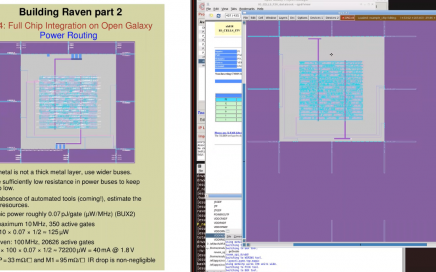

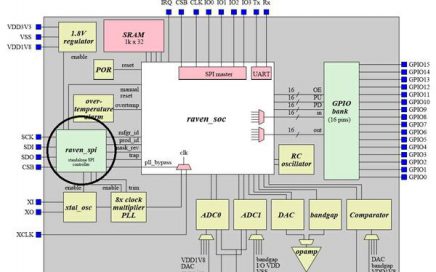

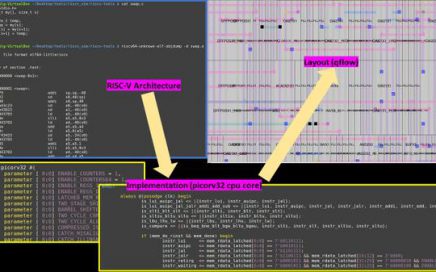

Since then, we have promoted courses using a lot of open-source EDA tools like Opentimer for STA, qflow for Physical design, TL-verilog for pipelining, Yosys for Synthesis, Proton for EDA and many more. Not only that, we have organized an online conference (as you might be aware) and here’s the link with details:

https://www.vlsisystemdesign.com/vsdopen2018-2/