Hello

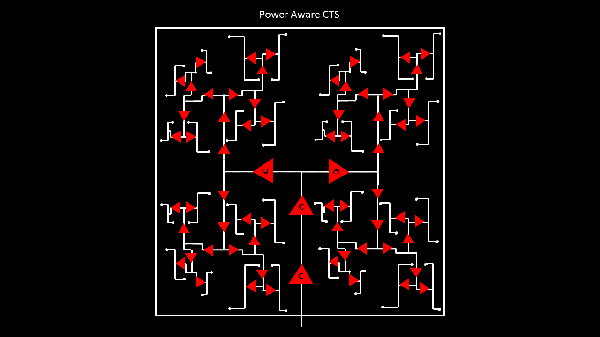

How about saving some power for the below clock tree network ?

It’s tricky and if we go with the right approach, we might end up saving almost ‘half’ of the power that the below clock network might take as of now. (Apologies to experts on this topic as I might go to very basic level, but I can guarantee that it would be interesting).

By the way, this technique can be used only under certain conditions where some parts of the chip remain silent, while the other part switches. Stay with me to know ‘how?’

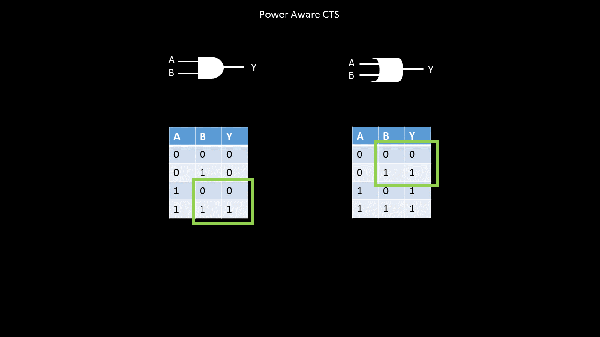

And, if I say, the solution lies in the functioning of below gates (already apologized to experts of this field for going to basics :)), you will be surprised to watch how we trick the clock network using handful below gates to reduce power significantly (at-least half)

There are many ways to view things. As an eg. you would view the above gates as AND/OR gates with 2 inputs A and B, but I would look the functioning of these gates as an opportunity to reduce power. How?

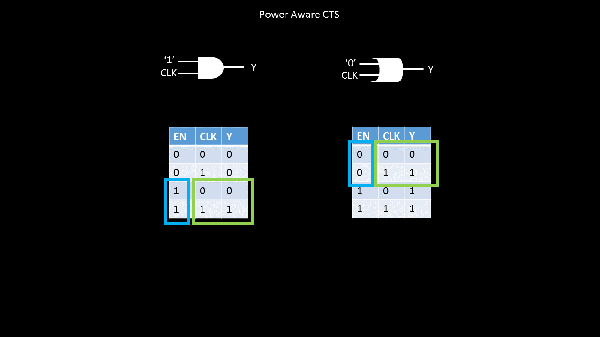

Look at the below image now, and you will realize that, if I hold one of the inputs at constant logic level, these gates will then behave like a simple buffer i.e. in both below cases, Y = CLK (like in a buffer Y = input)

So, I will call one input of the gates as ‘EN’ i.e. enable signal, and the other one as ‘CLK’. In case of an ‘AND’ gate, whenever ‘EN’ is high, and in case of OR gate whenever the ‘EN’ is low, the output ‘Y’ is ‘CLK’

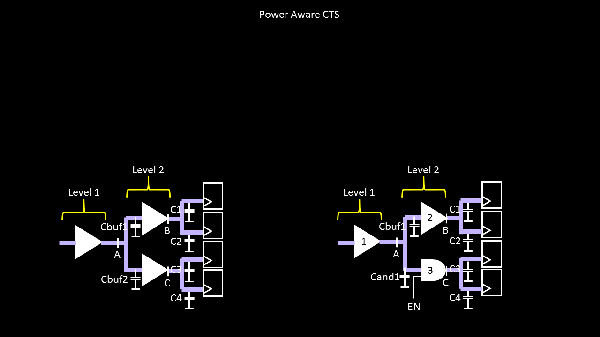

With these basics in place, next step is identify functionality for those parts of your chip which remain silent or do not function while another part of your chip, which functions.

If we are able to isolate these parts, we can combine that with above concepts and come up with a clock network which will potentially save huge power, in turn, which will help you save some battery on your mobile phones.

To nail the bigger picture, I will use the below small one to explain, what I mean by above statement

“The human brain must continue to frame the problems for the electronic machine to solve.” – David Sarnoff (1891 – 1971)

That’s exactly what I’ll do in my upcoming posts. Stay tuned 🙂

Regards

Kunal