Hello

Of course …. The biggest cost that I am mentioning about is the fab cost and that’s my biggest challenge to build better chips. We all know that. But let’s talk about of some real numbers and facts here

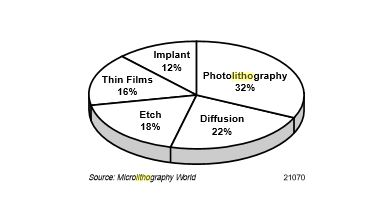

When mentioned about fab cost, lithography accounts for a major portion of it (almost 32%) as shown in below image[1]. Though it’s really important to know what is ‘photo lithography’, I will briefly explain this, while focus mainly on the history of rise in fabrication cost

Photo lithography is a process to transfer geometric pattern from mask to wafer surface through a light sensitive chemical called as photo resist. There could be about 30-50 mask layers and each mask goes through a photo lithography process to fabricate a complex chip onto a silicon wafer i.e. a wafer goes through ~30 to 50 cycles of photo lithography [2]

Above image represents the split of fabrication cost per wafer. But, while building a semiconductor fabrication facility, apart the photo lithography equipment taking major plunge in cost, wafer size also dominates the increasing cost of fabrication.

How’s that so? Let me briefly explain this

A round wafer can hold more than 1000 die’s where a ‘die’ represents a fully functional chip. Below image shows a wafer map where each blue square represents a ‘die’

Bigger the wafer, more the number of die’s that can be accommodated and higher the throughput. When we move from 4inch to 6inch, that’s an 2.25times increase in the wafer area. Now that’s an ‘equivalent’ increase in cost per wafer and hence cost per mask. Carefully look into the below equations [4]:

So in order to keep a fab profitable, it should constantly operate at high volumes. TSMC’s initiative to build ‘gigafab’ will process around 100K ‘300mm’ wafers per month [5]. High volumes definitely reduce unit costs but fixed costs of building fabs has hit sky high over the period of last 20 years

Overall, to build a fab in 1966, it costs around $14M, which had increased to $1.5B by 1995, and today the cost of building a leading edge fab will be around $6B [6]

That’s not all. To add to the overall cost, there is an additional cost involved to develop basic process flow at each node. Over the years, industry has moved on from 0.5um technology to 0.065um and even lesser (0.016um). There is a cost involved in developing a process for each node that adds up the total cost of building a fab. Below table carefully sums up the cost involved in developing a process technology and minimum revenue needed to achieve an ROI at each node [7]. It means that to achieve an ROI at, say 65nm node, a manufacturer must generate a total of $10B as revenue or sales [7].

![]()