Pre-place Cells and Power Ring Generation contest

Problem Statement– Today’s version of open-source EDA tools, work very well for hierarchical designs sub-25k instance count. For hierarchical designs ~500k instance count, participants are expected to develop code which will enable users to pre-place cells like macros/IP’s/memories inside core and create power rings around core and pre-placed cells

On successful completion, participants with best results will win:

- Certification and recognition from IIT Madras RISC-V SHAKTI Team

- 1 LIVE webinar with VSD team on this topic with 50% Lifetime Revenue share

Inputs given for code development and testing:

- A text file in DEF formatwith clear definitions of core/die width, pad placement and other unplaced cells

- Industry grade 180nm PDK’s (standard cells, memories, pads) LEF formats

Expected output from this contest:

A text file in standard DEF format which has all information about inputs which were provided + information about pre-placed cells and power rings (shown in below image)

Let me suggest you some steps to reach to above point:

Step 1) Find a way to parse input DEF file provided by VSD, which has locations, co-ordinates, instance names and many more information of all instances that you see in below image. It can be a command something like below

read_def <input_def_file>

If the DEF file syntax is not in par with standard DEF syntax, issue an error message specifying line number where there is a syntax error

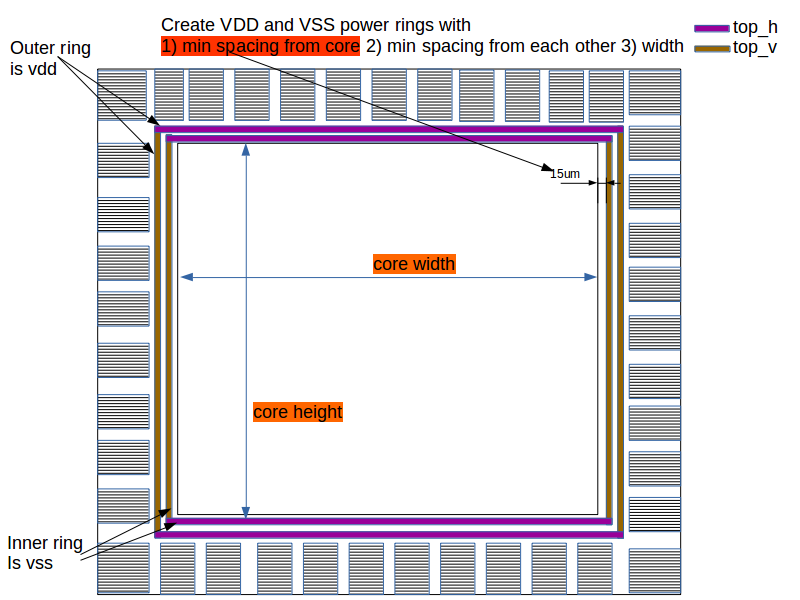

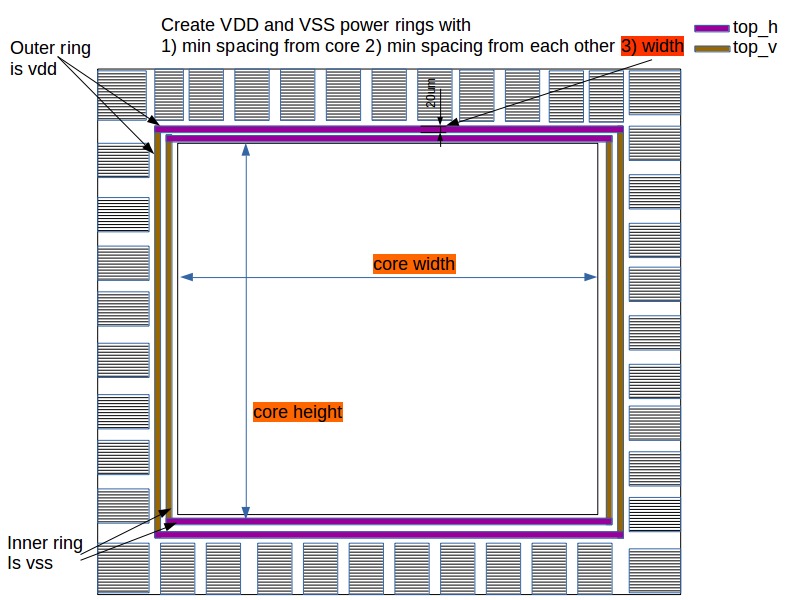

Step 2) Develop code (or command) to create VDD and VSS power rings around core with below options (See below images for description)

- min spacing from core

- min spacing from each other

- width

It can be a command something like below

create_power_rings_around_core -min_spacing_from_core <number_in_um> -min_spacing_from_nearby_layer <number_in_um> -width <number_in_um> -net_names {VDD VSS}

For “-net_names”, there should be an option to create multiple VDD and VSS. For eg. if -net_names {VDD VSS VDD VSS VDD} or -net_names {VDD VDD VSS VSS}, then the code should create 5 power/ground or 4 power/ground in order mentioned above. If spacing between core boundary and pad is not enough to fit 5 power/ground or 4 power/ground, please issue error message

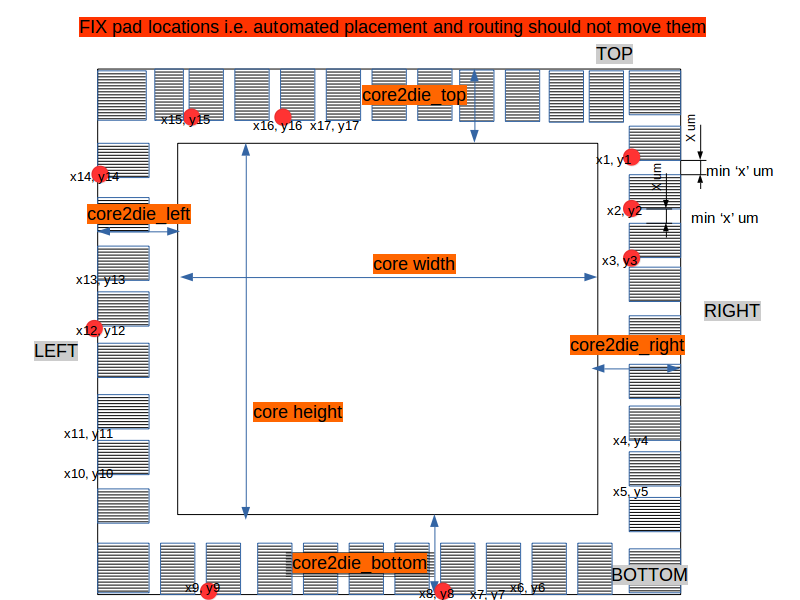

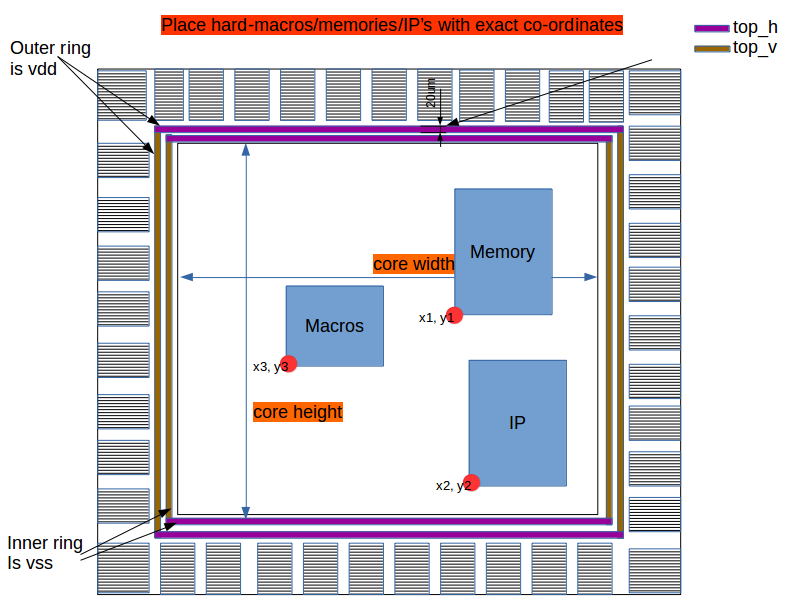

Step 3) Develop code (or command) to place macro’s, memories, IP’s inside core with exact co-ordinates and freeze its location such that, automated placement tools don’t move it (See below image for description). Keyword “FIXED” is used to define such cells in DEF file format (Look up for industry DEF file formats).

It can be a command something like below

pre_place_cell -cell <cell_name> -location <x_cordinate y_cordinate> -fixed <true/false>

User can use the command like below

pre_place_cell -cell <memory_name> -location <x1 y1> -fixed true

pre_place_cell -cell <macro_name> -location <x2 y2> -fixed true

pre_place_cell -cell <IP_name> -location <x3 y3> -fixed true

If <x1 y1>, <x2 y2> and <x3 y3> are outside core, please issue an error

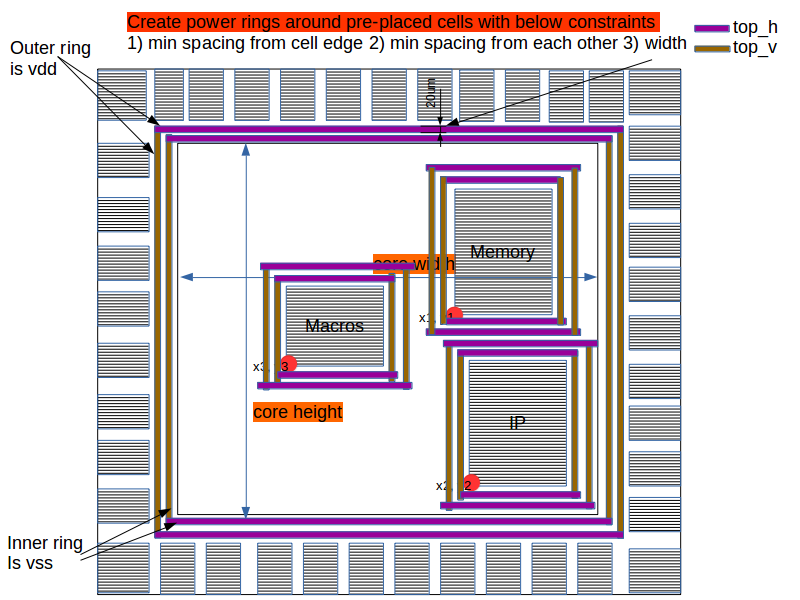

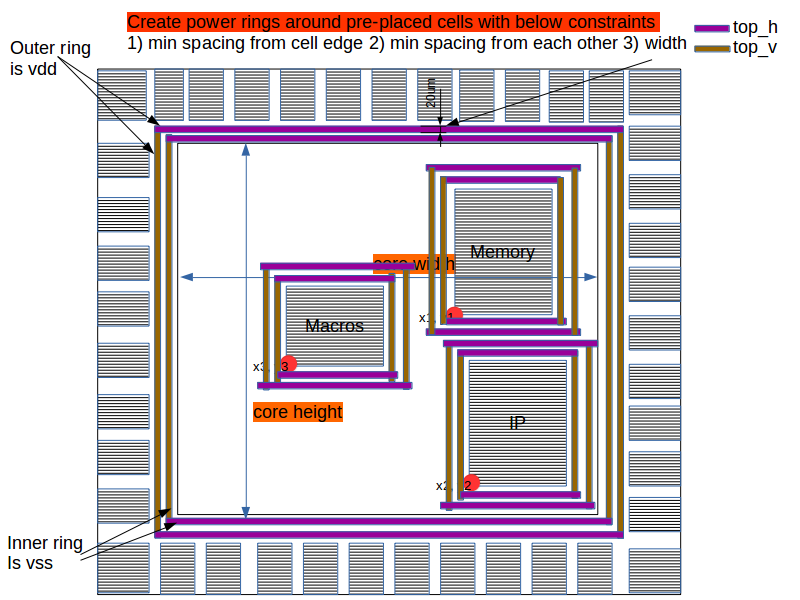

Step 4) Develop code (or command) to create power rings around macro’s/IP’s/memories OR any pre-placed cell with below options (See below image for description)

- min spacing from cell boundary

- min spacing from each other

- width

It can be a command something like below

create_power_rings_around_pre_placed_cell -min_spacing_from_cell_boundary <number_in_um> -min_spacing_from_nearby_layer <number_in_um> -width <number_in_um> -net_names {VDD VSS}

Terms and condition:

- You are free to use the source code of existing (and only) opensource tools like magic, qflow, graywolf, qrouter.

- Each line of your code needs to be open-sourced and documented