Hello

Let me quote “Winston S Churchill”, who said “A pessimist sees the difficulty in every opportunity; an optimist sees the opportunity in every difficulty.”

So pessimism is not good, and so is true for a timing path as well. 🙂

With On-Chip variation, we might introduce extra pessimism in clock path, common to launch and capture flop clock pins. How? I will get back to this in below post (or may be next one).

Our job, is to remove this pessimism and make a timing path analysis, close to a real one. How? I will get back to this, as well, in follow-up post

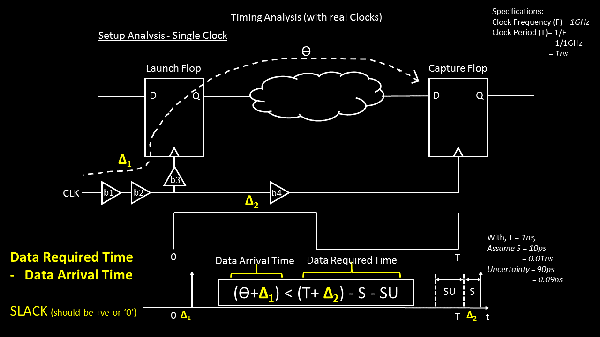

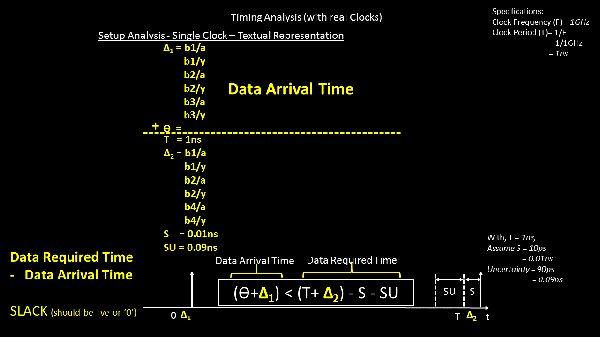

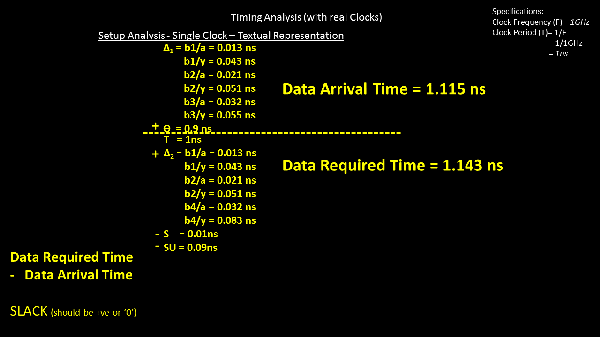

Let’s look into below image, to visualize how a real timing path looks like, what is data arrival, data required and slack. (for setup timing analysis)

S = library setup time, SU = setup uncertainty

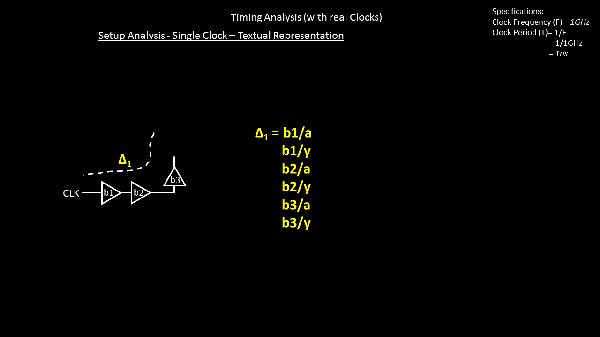

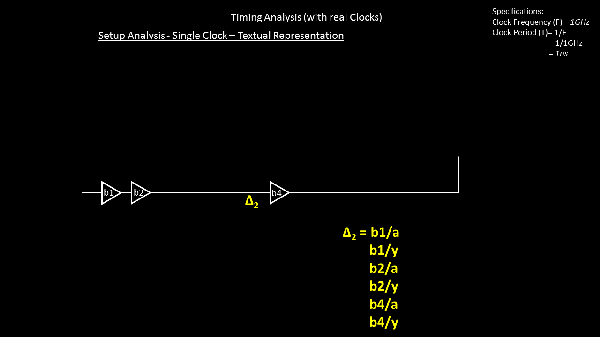

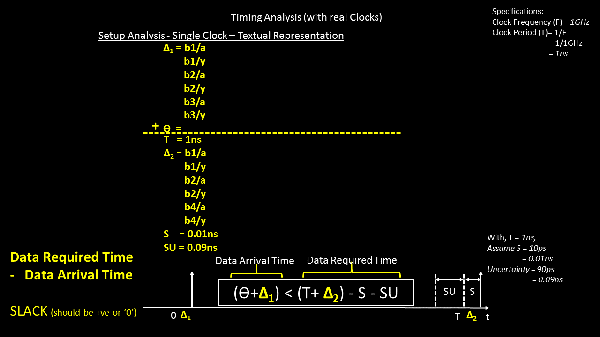

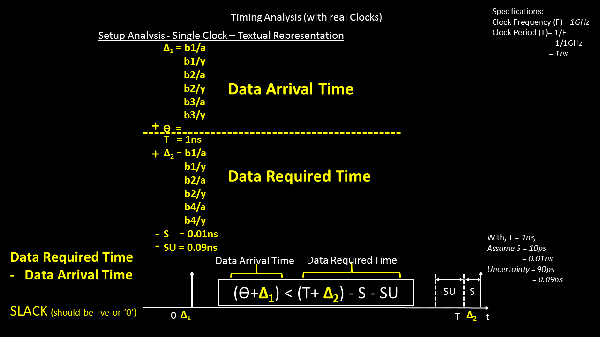

And below images are the textual conversion of above image. This is what you see in a standard timing report (we will focus on clock path for now, as that’s our point of concern)

Let’s structure the timing report in a understandable format as below

….(sentence continued from above) and the second half becomes you data required time

PS : may for homework, take a timing path in your real design, and see if the above makes sense

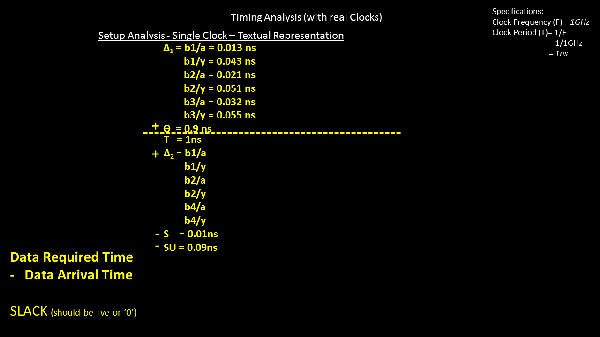

A timing report without real numbers, is like “A body without skeleton” 🙂.

Assuming below values for the cell and net delays (over here, net delay is the value on xyz/a and cell delay is the value on xyz/z)

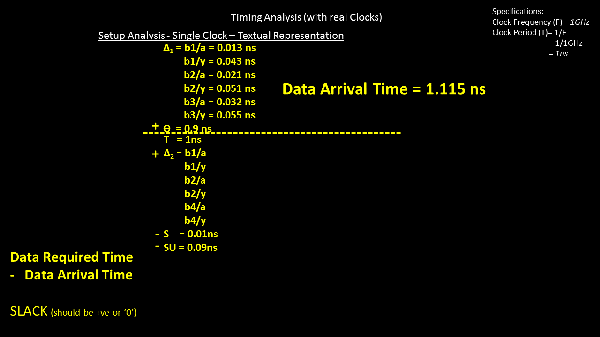

Data arrival time in this case is 1.115ns (nothing complex, just used a hand calculator)

Notice, b1 and b2 are common cells in launch and capture path. So while assuming numbers for capture clock path, the delay values for these cells will remain same as shown below.

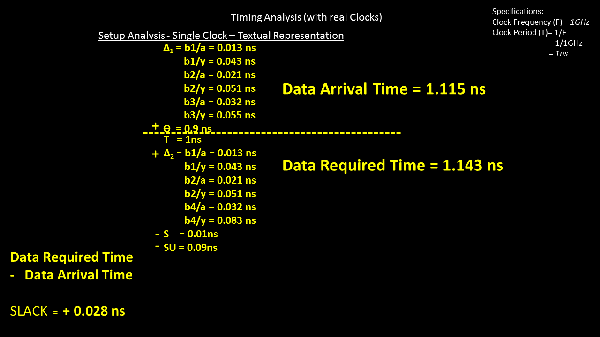

With that said, data required time will be 1.143ns and …… (continued after below image)

…… (continued from above) slack becomes +0.028ns

And I know, what it means for an STA engineer to see that positive slack 🙂

NEWS FLASH : We didn’t account for OCV yet 🙁

Let me give you sometime to absorb the above images, as they tell depict many important things. And I have seen this somewhere “If you want to walk fast, walk alone. If you want to walk far, walk together”

I want to go far 🙂 Let’s continue from this point in next post

Thanks

Kunal